### STM32F3 Technical Training

2013, CompelFest

**Alexander Kvashin**

**Roman Popov**

### Cortex-M processors

### Forget traditional 8/16/32-bit classifications

- Seamless architecture across all applications

- Every product optimised for ultra low power and ease of use

| Cortex-M0                       | Cortex-M3                | Cortex-M4                 |

|---------------------------------|--------------------------|---------------------------|

| <b>"8/16-bit</b> " applications | "16/32-bit" applications | "32-bit/DSC" applications |

### **Binary and tool compatible**

### Cortex-M processors binary compatible

| РКН    | QADD        | QADD16 QADD8           | QASX     | QDADD    | QDSUB    | QSAX          | QSUB          |

|--------|-------------|------------------------|----------|----------|----------|---------------|---------------|

| QSUB16 | QSUB8       | SADD16 SADD8           | SASX     | SEL      | SHADD16  | SHADD8        | SHASX         |

| SHSAX  | SHSUB16     | SHSUB8 SMLABE          | 3 SMLABT | SMLATB   | SMLATT   | SMLAD         | SMLALBB       |

|        |             |                        |          |          |          | SMLALBT       | SMLALTB       |

| ADC    | ADD         | ADR AND                | ASR      | В        | CLZ      | SMLALTT       | SMLALD        |

| BFC    | BFI         | BIC CDP                | CLREX    | CBNZ CBZ | CMN      | SMLAWB        | SMLAWT        |

| СМР    |             |                        | DBG      | EOR      | LDC      | SMLSD         | SMLSLD        |

| LDMIA  | BKPT BLX    | ADC ADD ADR            | LDMDB    |          | LDRB     | SMMLA         | SMMLS         |

| LDRBT  | BX CPS      | AND ASR B              | LDRD     |          | LDREXB   | SMMUL         | SMUAD         |

| LDREXH | DMB         | BL BIC                 | LDRH     |          | LDRSB    | SMULBB        | SMULBT        |

| LDRSBT | DSB         | CMN CMP EOR            | LDRSHT   | LDRSH    | LDRT     | SMULTB        | SMULTT        |

| MCR    | ISB         | LDR LDRB LDM           | LSL      |          | MLS      | SMULWB        | SMULWT        |

| MCRR   | MRS         | (LDRH) (LDRSB) (LDRSH) | MLA      | MOV      | MOVT     | SMUSD         | SSAT16        |

| MRC    | MSR         |                        | MRRC     | MUL      | MVN      | SSAX          | SSUB16        |

| NOP    | NOP REV     | MUL MVN ORR            | ORN      | ORR      | PLD      | SSUB8         | SXTAB         |

| PLDW   | REV16 REVSH | POP PUSH ROR           | PLI      | РОР      | PUSH     | SXTAB16       | SXTAH         |

| RBIT   | SEV SXTB    | RSB SBC STM            | REV      | REV16    | REVSH    | SXTB16        | UADD16        |

| ROR    | SXTH UXTB   | STR STRB STRH          | RRX      | RSB (    | SBC      | UADD8         | UASX          |

| SBFX   | UXTH WFE    | SUB SVC TST            | SDIV     | SEV      | SMLAL    | UHADD16       | UHADD8        |

| SMULL  | WFI YIELD   | CORTEX-M0/M1           | SSAT     | STC      | STMIA    | UHASX         | UHSAX         |

| STMDB  |             |                        | STR      | STRB     | STRBT    | UHSUB16       | UHSUB8        |

| STRD   | STREX       | STREXB STREXH          | STRH     | STRHT    | STRT     | UMAAL         | UQADD16       |

| SUB    | SXTB        | SXTH TBB               | ТВН      | TEQ      | TST      | UQADD8        | UQASX         |

| UBFX   |             | UMLAL                  | USAT     | UXTB     | UXTH     | UQSAX         | UQSUB16       |

| WFE    | WFI         | YIELD IT               |          | CC       | DRTEX-M3 | UQSUB8        | USAD8         |

|        |             |                        |          |          |          | USADA8        | USAT16        |

| USAX   | USUB16      | USUB8 UXTAB            | UXTAB16  | UXTAH    | UXTB16   |               | Cortex-M4     |

| VABS   | VADD        | VCMP VCMPE             |          |          |          | VLDM<br>VNMLA | VLDR<br>VNMLS |

|        | VPOP        | VPUSH VSQRT            |          |          | VSUB     |               | Cortex-M4F    |

10

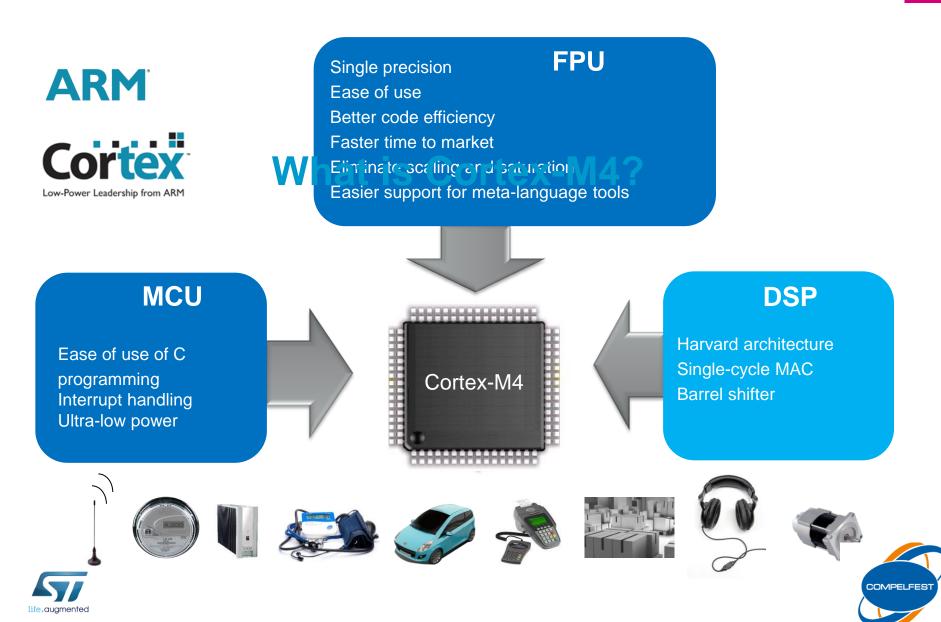

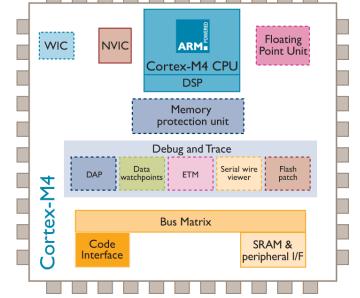

### ARM Cortex M4 Core

# Cortex-M4 processor microarchitecure

#### ARMv7ME Architecture

- Thumb-2 Technology

- DSP and SIMD extensions

- Single cycle MAC (Up to 32 x 32 + 64 -> 64)

- Optional single precision FPU

- Integrated configurable NVIC

- Compatible with Cortex-M3

#### Microarchitecture

- 3-stage pipeline with branch speculation

- 3x AHB-Lite Bus Interfaces

#### Configurable for ultra low power

- Deep Sleep Mode, Wakeup Interrupt Controller

- Power down features for Floating Point Unit

#### Flexible configurations for wider applicability

- Configurable Interrupt Controller (1-240 Interrupts and Priorities)

- Optional Memory Protection Unit

- Optional Debug & Trace

12

life.augmented

### Cortex-M feature set comparison 13

|                               | Cortex-M0                             | Cortex-M3       | Cortex-M4                         |  |

|-------------------------------|---------------------------------------|-----------------|-----------------------------------|--|

| Architecture Version          | V6M                                   | v7M             | v7ME                              |  |

| Instruction set architecture  | Thumb, Thumb-2<br>System Instructions | Thumb + Thumb-2 | Thumb + Thumb-2,<br>DSP, SIMD, FP |  |

| DMIPS/MHz                     | 0.9                                   | 1.25            | 1.25                              |  |

| Bus interfaces                | 1                                     | 3               | 3                                 |  |

| Integrated NVIC               | Yes                                   | Yes             | Yes                               |  |

| Number interrupts             | 1-32 + NMI                            | 1-240 + NMI     | 1-240 + NMI                       |  |

| Interrupt priorities          | 4                                     | 8-256           | 8-256                             |  |

| Breakpoints, Watchpoints      | 4/2/0, 2/1/0                          | 8/4/0, 2/1/0    | 8/4/0, 2/1/0                      |  |

| Memory Protection Unit (MPU)  | No                                    | Yes (Option)    | Yes (Option)                      |  |

| Integrated trace option (ETM) | No                                    | Yes (Option)    | Yes (Option)                      |  |

| Fault Robust Interface        | No                                    | Yes (Option)    | No                                |  |

| Single Cycle Multiply         | Yes (Option)                          | Yes             | Yes                               |  |

| Hardware Divide               | No                                    | Yes             | Yes                               |  |

| WIC Support                   | Yes                                   | Yes             | Yes                               |  |

| Bit banding support           | No                                    | Yes             | Yes                               |  |

| Single cycle DSP/SIMD         | No                                    | No              | Yes                               |  |

| Floating point hardware       | No                                    | No              | Yes                               |  |

| Bus protocol                  | AHB Lite                              | AHB Lite, APB   | AHB Lite, APB                     |  |

| CMSIS Support                 | Yes                                   | Yes             | Yes                               |  |

### Cortex-M processors binary compatible

|        |             |               |        |         |          |          |          |              | 1                             |

|--------|-------------|---------------|--------|---------|----------|----------|----------|--------------|-------------------------------|

| РКН    | QADD        | QADD16        | QADD8  | QASX    | QDADD    | QDSUB    | QSAX     | QSUB         |                               |

| QSUB16 | QSUB8       | SADD16        | SADD8  | SASX    | SEL      | SHADD16  | SHADD8   | SHASX        |                               |

| SHSAX  | SHSUB16     | SHSUB8        | SMLABB | SMLABT  | SMLATB   | SMLATT   | SMLAD    | SMLALBB      |                               |

|        |             |               |        |         |          |          | SMLALBT  | SMLALTB      |                               |

| ADC    | ADD         | ADR           | AND    | ASR     | В        | CLZ      | SMLALTT  | SMLALD       |                               |

| BFC    | BFI         | BIC           |        | CLREX   | CBNZ CBZ |          | SMLAWB   | SMLAWT       |                               |

| СМР    |             |               |        | DBG     | EOR      |          | SMLSD    | SMLSLD       |                               |

|        | BKPT BLX    | ADC ADD       |        | LDMDB   |          | LDRB     | SMMLA    | SMMLS        |                               |

| LDRBT  | BX CPS      | AND ASR       |        | LDRD    |          | LDREXB   | SMMUL    | SMUAD        |                               |

| LDREXH | DMB         |               |        | LDRH    |          | LDRSB    | SMULBB   | SMULBT       |                               |

| LDRSBT | DSB         |               | EOR    | LDRSHT  | LDRSH    |          | SMULTB   | SMULTT       |                               |

| MCR    | ISB         |               |        | LSL     | LSR      | MLS      | SMULWB   | SMULWT       |                               |

| MCRR   | MRS         | (LDRH) (LDRSB |        | MLA     | MOV      | MOVT     | SMUSD    | SSAT16       |                               |

| MRC    | MSR         |               |        | MRRC    | MUL      | MVN      | SSAX     | SSUB16       | Cortex                        |

| NOP    | NOP REV     |               |        | ORN     | ORR      | PLD      | SSUB8    | SXTAB        | Cortex                        |

| PLDW   | REV16 REVSH |               |        | PLI     | РОР      | PUSH     | SXTAB16  | SXTAH        |                               |

| RBIT   | SEV SXTB    | RSB SBC       |        | REV     | REV16    | REVSH    | SXTB16   | UADD16       | Low-Power Leadership from ARM |

| ROR    | SXTH UXTB   | STR STRB      | (STRH) | RRX     | RSB      | SBC      | UADD8    | UASX         |                               |

| SBFX   | UXTH WFE    |               |        | SDIV    | SEV      | SMLAL    | UHADD16  | UHADD8       |                               |

| SMULL  | WFI YIELD   | CORTEX-       | M0/M1  | SSAT    | STC      | STMIA    | UHASX    | UHSAX        |                               |

| STMDB  |             |               |        | STR     | STRB     | STRBT    | UHSUB16  | UHSUB8       |                               |

| STRD   | STREX       | STREXB        | STREXH | STRH    | STRHT    | STRT     | UMAAL    | UQADD16      |                               |

| SUB    | SXTB        | SXTH          | твв    | твн     | TEQ      | TST      | UQADD8   | UQASX        |                               |

| UBFX   |             | UMLAL         |        | USAT    | UXTB     |          | UQSAX    | UQSUB16      |                               |

| WFE    | WFI         |               | T      |         | С        | ORTEX-M3 | UQSUB8   | USAD8        |                               |

|        |             |               |        |         |          |          | USADA8   | USAT16       |                               |

| USAX   | USUB16      | USUB8         | UXTAB  | UXTAB16 | UXTAH    | UXTB16   |          | Cortex-M4    |                               |

|        |             |               |        |         |          |          |          |              | ]                             |

| VABS   | VADD        | VCMP          | VCMPE  | VCVT    |          |          |          |              |                               |

| VMLA   |             |               | VMRS   | VMSR    |          |          |          |              |                               |

| VNMUL  |             | VPUSH         | VSQRT  | VSTM    |          |          |          | Cortex-M4F   |                               |

|        |             |               |        |         |          |          | <u> </u> | COILEX-IMI4F |                               |

|        |             |               |        |         |          |          |          |              | COMPELFEST                    |

|        |             |               |        |         |          |          |          |              | COMPELFEST                    |

15

### Cortex-M4 overview 16

#### Main Cortex-M4 processor features

- ARMv7-ME architecture revision

- Fully compatible with Cortex-M3 instruction set

- Single-cycle multiply-accumulate (MAC) unit

- Optimized single instruction multiple data (SIMD) instructions

- Saturating arithmetic instructions

- Optional single precision Floating-Point Unit (FPU)

- Hardware Divide (2-12 Cycles), same as Cortex-M3

- Barrel shifter (same as Cortex-M3)

# Single-cycle multiply-accumulate unit 17

- The multiplier unit allows any MUL or MAC instructions to be executed in a single cycle

- Signed/Unsigned Multiply

- Signed/Unsigned Multiply-Accumulate

- Signed/Unsigned Multiply-Accumulate Long (64-bit)

- Benefits : Speed improvement vs. Cortex-M3

- 4x for 16-bit MAC (dual 16-bit MAC)

- 2x for 32-bit MAC

- up to 7x for 64-bit MAC

### Cortex-M4 extended single cycle MAC 18

| OPERATION                                     | INSTRUCTIONS                       | CM3 | CM4 |

|-----------------------------------------------|------------------------------------|-----|-----|

| 16 x 16 = 32                                  | SMULBB, SMULBT, SMULTB, SMULTT     | n/a | 1   |

| 16 x 16 + 32 = 32                             | SMLABB, SMLABT, SMLATB, SMLATT     | n/a | 1   |

| 16 x 16 + 64 = 64                             | SMLALBB, SMLALBT, SMLALTB, SMLALTT | n/a | 1   |

| $16 \times 32 = 32$                           | SMULWB, SMULWT                     | n/a | 1   |

| $(16 \times 32) + 32 = 32$                    | SMLAWB, SMLAWT                     | n/a | 1   |

| $(16 \times 16) \pm (16 \times 16) = 32$      | SMUAD, SMUADX, SMUSD, SMUSDX       | n/a | 1   |

| $(16 \times 16) \pm (16 \times 16) + 32 = 32$ | SMLAD, SMLADX, SMLSD, SMLSDX       | n/a | 1   |

| $(16 \times 16) \pm (16 \times 16) + 64 = 64$ | SMLALD, SMLALDX, SMLSLD, SMLSLDX   | n/a | 1   |

| $32 \times 32 = 32$                           | MUL                                | 1   | 1   |

| $2 \pm (32 \times 32) = 32$                   | MLA, MLS                           | 2   | 1   |

| $32 \times 32 = 64$                           | SMULL, UMULL                       | 5-7 | 1   |

| $(32 \times 32) + 64 = 64$                    | SMLAL, UMLAL                       | 5-7 | 1   |

| $(32 \times 32) + 32 + 32 = 64$               | UMAAL                              | n/a | 1   |

| 32 ± (32 x 32) = 32 (upper)                   | SMMLA, SMMLAR, SMMLS, SMMLSR       | n/a | 1   |

| (32 x 32) = 32 (upper)                        | SMMUL, SMMULR                      | n/a | 1   |

All the above operations are single cycle on the Cortex-M4 processor

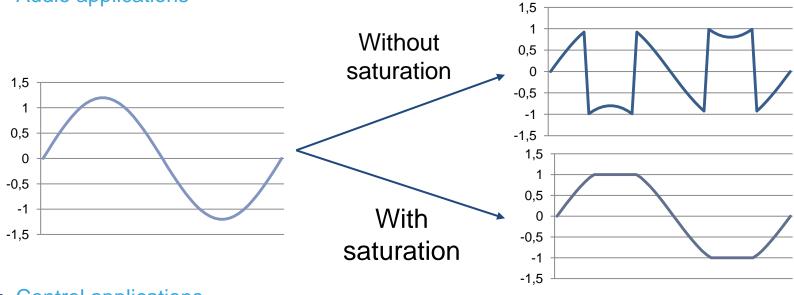

# Saturated arithmetic

Intrinsically prevents overflow of variable by clipping to min/max boundaries and remove CPU burden due to software range checks

#### Benefits

Audio applications

- Control applications

- The PID controllers' integral term is continuously accumulated over time. The saturation automatically limits its value and saves several CPU cycles per regulators

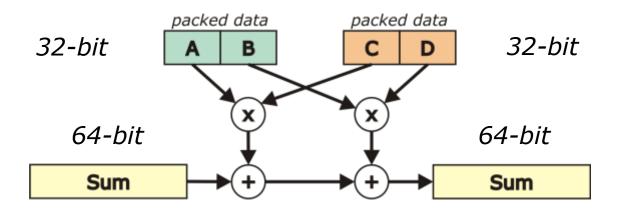

# Single-cycle SIMD instructions 20

- Stands for <u>Single Instruction Multiple Data</u>

- Allows to do simultaneously several operations with 8-bit or 16-bit data format

- Ex: dual 16-bit MAC (Result = 16x16 + 16x16 + 32)

- Ex: Quad 8-bit SUB / ADD

#### Benefits

- Parallelizes operations (2x to 4x speed gain)

- Minimizes the number of Load/Store instruction for exchanges between memory and register file (2 or 4 data transferred at once), if 32-bit is not necessary

- Maximizes register file use (1 register holds 2 or 4 values)

### SIMD operation example 21

SIMD extensions perform multiple operations in one cycle

Sum = Sum + (A x C) + (B x D)

SIMD techniques operate with packed data

# Cortex-M4 DSP instructions compared 22

|                |                                    | Cycle     | counts    |

|----------------|------------------------------------|-----------|-----------|

| CLASS          | INSTRUCTION                        | CORTEX-M3 | Cortex-M4 |

| Arithmetic     | ALU operation (not PC)             | 1         | 1         |

|                | ALU operation to PC                | 3         | 3         |

|                | CLZ                                | 1         | 1         |

|                | QADD, QDADD, QSUB, QDSUB           | n/a       | 1         |

|                | QADD8, QADD16, QSUB8, QSUB16       | n/a       | 1         |

|                | QDADD, QDSUB                       | n/a       | 1         |

|                | QASX, QSAX, SASX, SSAX             | n/a       | 1         |

|                | SHASX, SHSAX, UHASX, UHSAX         | n/a       | 1         |

|                | SADD8, SADD16, SSUB8, SSUB16       | n/a       | 1         |

|                | SHADD8, SHADD16, SHSUB8, SHSUB16   | n/a       | 1         |

|                | UQADD8, UQADD16, UQSUB8, UQSUB16   | n/a       | 1         |

|                | UHADD8, UHADD16, UHSUB8, UHSUB16   | n/a       | 1         |

|                | UADD8, UADD16, USUB8, USUB16       | n/a       | 1         |

|                | UQASX, UQSAX, USAX, UASX           | n/a       | 1         |

|                | UXTAB, UXTAB16, UXTAH              | n/a       | 1         |

|                | USAD8, USADA8                      | n/a       | 1         |

| Multiplication | MUL, MLA                           | 1 - 2     | 1         |

|                | MULS, MLAS                         | 1 - 2     | 1         |

|                | SMULL, UMULL, SMLAL, UMLAL         | 5 - 7     | 1         |

|                | SMULBB, SMULBT, SMULTB, SMULTT     | n/a       | 1         |

|                | SMLABB, SMLBT, SMLATB, SMLATT      | n/a       | 1         |

|                | SMULWB, SMULWT, SMLAWB, SMLAWT     | n/a       | 1         |

|                | SMLALBB, SMLALBT, SMLALTB, SMLALTT | n/a       | 1         |

|                | SMLAD, SMLADX, SMLALD, SMLALDX     | n/a       | 1         |

|                | SMLSD, SMLSDX                      | n/a       | 1         |

|                | SMLSLD, SMLSLD                     | n/a       | 1         |

|                | SMMLA, SMMLAR, SMMLS, SMMLSR       | n/a       | 1         |

|                | SMMUL, SMMULR                      | n/a       | 1         |

|                | SMUAD, SMUADX, SMUSD, SMUSDX       | n/a       | 1         |

|                | UMAAL                              | n/a       | 1         |

| Division       | SDIV, UDIV                         | 2 - 12    | 2 - 12    |

### Cortex-M4 non–DSP instructions 23

|              |                                  | Cycle     | counts    |

|--------------|----------------------------------|-----------|-----------|

| CLASS        | INSTRUCTION                      | CORTEX-M3 | Cortex-M4 |

| Load/Store   | Load single byte to R0-R14       | 1 - 3     | 1 - 3     |

|              | Load single halfword to R0-R14   | 1 - 3     | 1 - 3     |

|              | Load single word to R0-R14       | 1 - 3     | 1 - 3     |

|              | Load to PC                       | 5         | 5         |

|              | Load double-word                 | 3         | 3         |

|              | Store single word                | 1 - 2     | 1 - 2     |

|              | Store double word                | 3         | 3         |

|              | Load-multiple registers (not PC) | N+1       | N+1       |

|              | Load-multiple registers plus PC  | N+5       | N+5       |

|              | Store-multiple registers         | N+1       | N+1       |

|              | Load/store exclusive             | 2         | 2         |

|              | SWP                              | n/a       | n/a       |

| Branch       | B, BL, BX, BLX                   | 2 - 3     | 2 - 3     |

|              | CBZ, CBNZ                        | 3         | 3         |

|              | ТВВ, ТВН                         | 5         | 5         |

|              | IT                               | 0 - 1     | 0 - 1     |

| Special      | MRS                              | 1         | 1         |

|              | MSR                              | 1         | 1         |

|              | CPS                              | 1         | 1         |

| Manipulation | BFI, BFC                         | 1         | 1         |

|              | RBIT, REV, REV16, REVSH          | 1         | 1         |

|              | SBFX, UBFX                       | 1         | 1         |

|              | UXTH, UXTB, SXTH, SXTB           | 1         | 1         |

|              | SSAT, USAT                       | 1         | 1         |

|              | SEL                              | n/a       | 1         |

|              | SXTAB, SXTAB16, SXTAH            | n/a       | 1         |

|              | UXTB16, SXTB16                   | n/a       | 1         |

|              | SSAT16, USAT16                   | n/a       | 1         |

|              | РКНТВ, РКНВТ                     | n/a       | 1         |

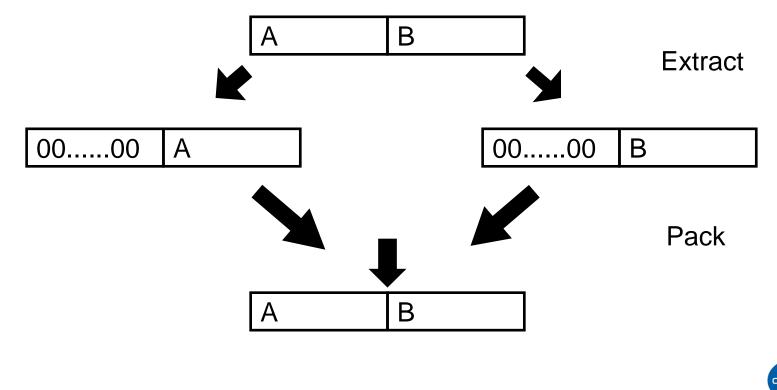

### Packed data types 24

OMPELFES

- Several instructions operate on "packed" data types

- Byte or halfword quantities packed into words

- Allows more efficient access to packed structure types

- SIMD instructions can act on packed data

- Instructions to extract and pack data

### DSP performances for control application

- Example based on a complex formula used for sensorless motor drive

- Gain comes for load operations and SIMD instructions

- Total gain on this part is 25 to 35%

| Cortex M3 (28-38 c.) | Cortex M4 (18-28 c.)                                                                                  |

|----------------------|-------------------------------------------------------------------------------------------------------|

| LDRSH R12,[R4, #+12] | LDR R10,[R4, #+12]                                                                                    |

| LDRSH R0,[SP, #+20]  | (1 single 32-bit load replacing two 16-bit load with sign extension. <u>Gain: 2 cycles</u>            |

| SXTH LR,R8           |                                                                                                       |

| MUL R8,LR,R0         |                                                                                                       |

| LDR R1,[R4, #+44]    |                                                                                                       |

| SDIV R0,R1,R7        |                                                                                                       |

| LDRSH R2,[R4, #+24]  |                                                                                                       |

| LDRSH R3,[R4, #+26]  | LDR R2,[R4, #+22]                                                                                     |

| LDRSH R10,[R4, #+22] | (1 single 32-bit load replacing to 16-bit with sign extension. <u>Gain: 2 cycles)</u>                 |

| SXTH R6,R6           |                                                                                                       |

| MLS R5,R6,R10,R5     | *                                                                                                     |

| MLA R5,R9,R12,R5     | SMLSD R5, R10, R6, R5<br>(1 SIMD instruction replacing two multiply-<br>accumulate. Gain: 3 cycles)   |

| ASR R6,R8,#+15       |                                                                                                       |

| MLA R5,R6,R3,R5      |                                                                                                       |

| SXTH R0,R0           |                                                                                                       |

| MLS R5,R0,R2,R5      | SMLSD R5, R0, R2<br>(1 SIMD instruction replacing two multiply-<br>accumulate. <u>Gain: 3 cycles)</u> |

| STR R5,[SP, #+12]    |                                                                                                       |

|                      |                                                                                                       |

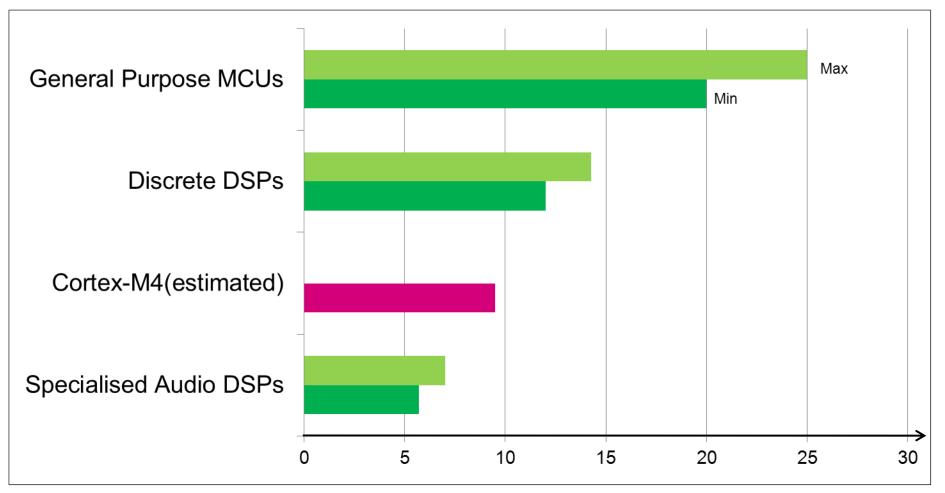

### DSP application example: MP3 audio playback

MHz required for MP3 decode (smaller is better !)

DSP concept from ARM (\*)

# DSP lib provided for free by ARM 27

#### • The benefits of software libraries for Cortex-M4

- Enables end user to develop applications faster

- · Keeps end user abstracted from low level programming

- Benchmarking vehicle during system development

- Clear competitive positioning against incumbent DSP/DSC offerings

- Accelerate third party software development

- Keeping it easy to access for end user

- Minimal entry barrier very easy to access and use

#### • One standard library – no duplicated efforts

- ARM channels effort/resources with software partner

- Value add through another level of software eg: filter config tools

### DSP lib function list snapshot 28

- Basic math vector mathematics | PID Controller

- Fast math sin, cos, sqrt etc

- Interpolation linear, bilinear

- Complex math

- Statistics max, min, RMS etc

- Filtering IIR, FIR, LMS etc

- Transforms FFT(real and complex), Cosine transform etc

- Matrix functions

Support functions – copy/fill arrays, data type conversions etc

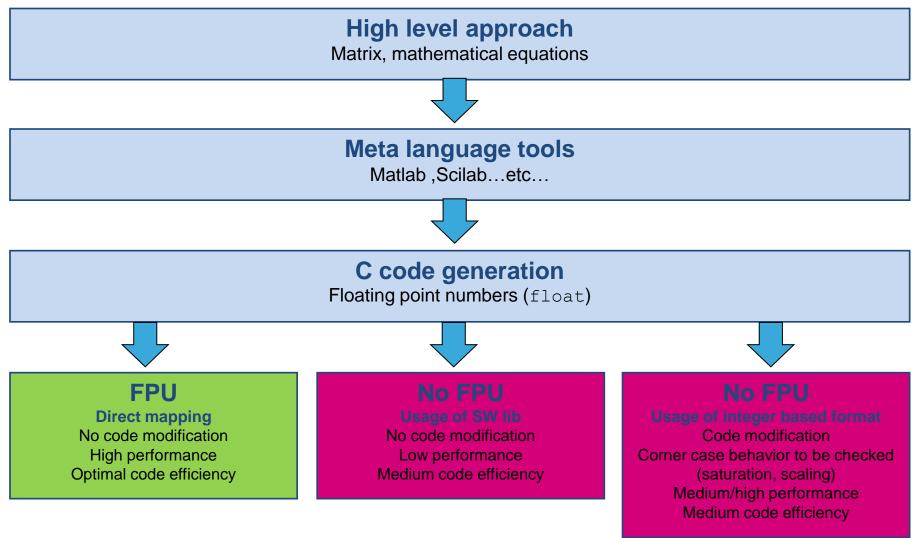

### Tools 29

#### Matlab / Simulink

- Embedded coder for code generation

- Mathworks

- Demo being developed (availability end of year)

- Aimagin (Rapidstm32)

#### Filter design tools

- Lot of tools available, most of them commercial product, some with low-cost offer, few free

- http://www.dspguru.com/dsp/links/digital-filter-design-software

### Overview

- Handles "real" number computation

- Standardized by IEEE.754-2008

- Number format

- Arithmetic operations

- Number conversion

- Special values

- 4 rounding modes

- 5 exceptions and their handling

### ARM Cortex-M FPU ISA

- Supports

- Add, subtract, multiply, divide

- Multiply and accumulate

- Square root operations

# Floating Point Unit 73

#### Introduction

- FPU usage

- Historical perspective

- Benefit of floating point arithmetic

- Example & performances

- Rounding issues

- IEEE 754

- ARM FPv4-SP Single Precision FPU

### FPU usage

### Historical perspective 75

- Usage of floating point as always been a need for computers since the beginning (Konrad Zuse - 1935)

- But the complexity of implementation discarded their usage during decades (IBM 704 - 1956)

- Floating point unit where implemented in mainframes with various coding techniques depending of the manufacturer

- IBM PC where designed to have floating point capabilities through optional **arithmetic coprocessors** (80x87 series)

- The standardization of floating point coding was done in the 80's through the IEEE 754 standard in 1985

• The Intel 80387 was the first intel coprocessor to implement the full TEEE 754 standard in 1987

# Benefits of a Floating-Point Unit 76

FPU allows to handled "real" numbers (C float) without penalty

#### If no FPU

- Need to emulate it by software

- Need to rework all its algorithm and fixed point implementation to handle scaling and saturation issues

#### FPU eases usage of high-level design tools (MatLab/Simulink)

- Now part of microcontroller development flow for advanced applications.

- Derivate code directly using native floating point leads to :

- quicker time to market (faster development)

- easy code maintenance

- more reliable application code as no post modification are needed (no critical scaling operations to move to fixed point)

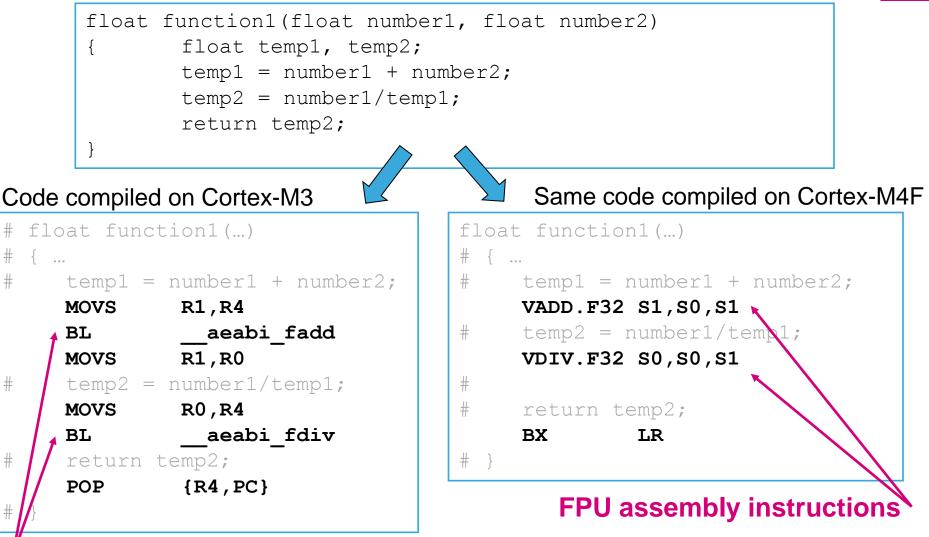

### C language example

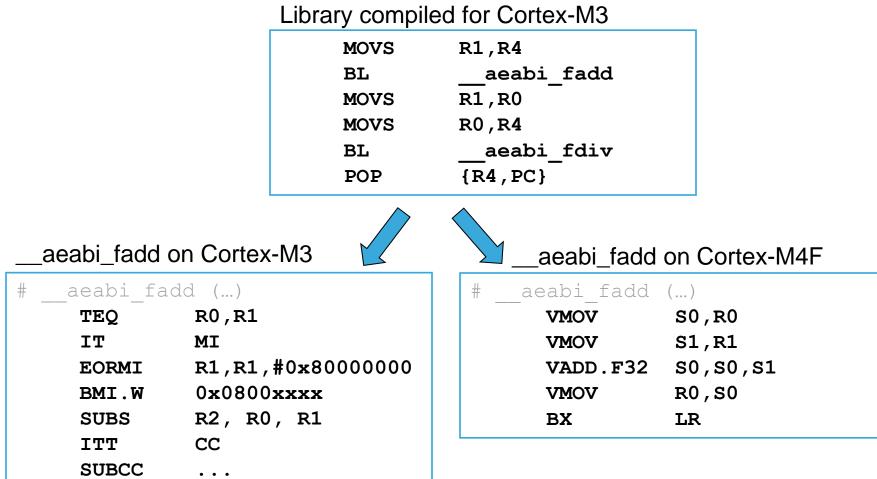

### Binary library example 78

. . .

Reduced code size & Enhanced performances

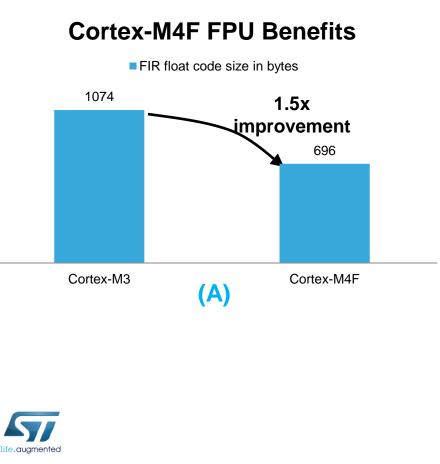

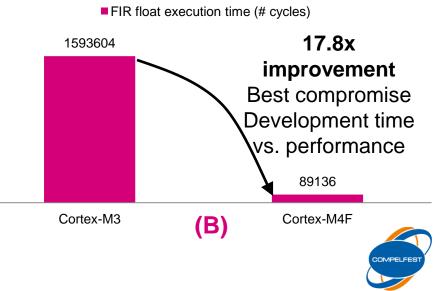

### Benefits of a Floating-Point Unit 79

- Comparison for a 166 coefficient FIR on float 32 with and without FPU (CMSIS library)

- Improvement in code size (A)

- Improvement in performance (B)

### Cortex-M4 : Floating point unit Features

- Single precision FPU

- Conversion between

- Integer numbers

- Single precision floating point numbers

- Half precision floating point numbers

- Handling floating point exceptions (Untrapped)

### Dedicated registers

- 16 single precision registers (S0-S15) which can be viewed as 16 Doubleword registers for load/store operations (D0-D7)

- FPSCR for status & configuration

80

### Rounding issues

#### The precision has some limits

• Rounding errors can be accumulated along the various operations an may provide unaccurate results (do not do financial operations with floatings...)

#### Few examples

- If you are working on two numbers in different base, the hardware automatically « denormalize » on of the two number to make the calculation in the same base

- If you are substracting two numbers very closed you are loosing the relative precision (also called cancellation error)

- If you are « reorganizing » the various operations, you may not obtain the same result as because of the rounding errors...

- Value1 = ((2.0f 1.99f) 0.01f); /\* Value1 = -9.313266E-9 \*/

- Value2 = (2.0f (1.99f + 0.01f)); /\* Value2 = 0 \*/

# Floating Point Unit 33

#### Introduction

#### • IEEE 754

- Number format

- Arithmetic operations

- Number conversion

- Special values

- 4 rounding modes

- 5 exceptions and their handling

- ARM FPv4-SP Single Precision FPU

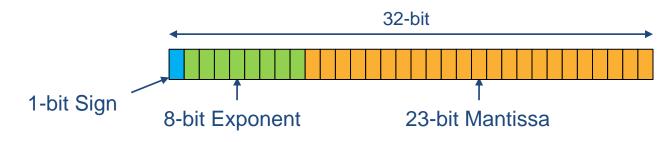

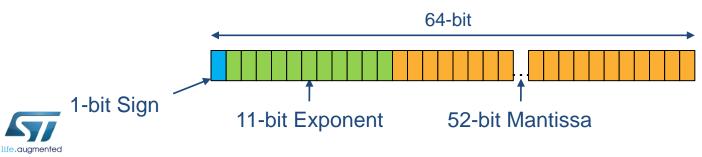

### Number format

### 3 fields

- Sign

- Biased exponent (sum of an exponent plus a constant bias)

- Fractions (or mantissa)

### Single precision : 32-bit coding

Double precision : 64-bit coding

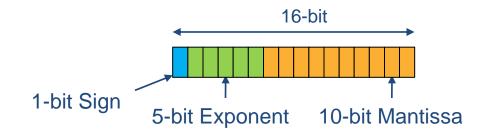

### Number format 85

#### Half precision : 16-bit coding

- Can also be used for storage in higher precision FPU

- ARM has an alternative coding for Half precision

## Normalized number value

#### Normalized number

Code a number as :

A sign + Fixed point number between 1.0 and 2.0 multiplied by  $2^{N}$

#### Sign field (1-bit)

- 0 : positive

- 1 : negative

#### Single precision exponent field (8-bit)

- Exponent range : 1 to 254 (0 and 255 reserved)

- Bias : 127

- Exponent bias range : -126 to +127

#### Single precision fraction (or mantissa) (23-bit)

- Fraction : value between 0 and 1 :  $\sum (N_i \cdot 2^{-i})$  with i in 1 to 24 range

- The 23 N<sub>i</sub> values are store in the fraction field

$(-1)^{s} \times (1 + \sum (N_{i} \cdot 2^{-i})) \times 2^{exp-bias}$

### Number value 87

#### Single precision coding of -7

- **Sign bit** = 1

- 7 = 1.75 x 4 =  $(1 + \frac{1}{2} + \frac{1}{4})$  x 4 =  $(1 + \frac{1}{2} + \frac{1}{4})$  x 2<sup>2</sup> =  $(1 + 2^{-1} + 2^{-2})$  x 2<sup>2</sup>

- **Exponent** = 2 + bias = 2 + 127 = 129 = 0b10000001

#### Result

- Hexadecimal value : 0xC0E00000

## Special values **88**

- Denormalized (Exponent field all "0", Mantisa non 0)

- Too small to be normalized (but some can be normalized afterward)

- $(-1)^{s} \times (\sum (N_{i}.2^{-i}) \times 2^{-bias})$

- Infinity (Exponent field "all 1", Mantissa "all 0")

- Signed

- Created by an overflow or a division by 0

- Can not be an operand

#### Not a Number : NaN (Exponent filed "all1", Mantisa non 0)

- Quiet NaN : propagated through the next operations (ex: 0/0)

- Signalled NaN : generate an error

#### Signed zero

Signed because of saturation

## Summary of IEEE 754 number coding

| Sign | Exponent   | Mantissa  | Number              |  |

|------|------------|-----------|---------------------|--|

| 0    | 0          | 0         | +0                  |  |

| 1    | 0          | 0         | -0                  |  |

| 0    | Мах        | 0         | +00                 |  |

| 1    | Мах        | 0         | -00                 |  |

| -    | Мах        | !=0 MSB=1 | QNaN                |  |

| -    | Мах        | !=0 MSB=0 | SNaN                |  |

| -    | 0          | !=0       | Denormalized number |  |

| -    | [1, Max-1] | -         | Normalized number   |  |

## Floating-point rounding

#### Round to nearest

- Default rounding mode

- If the two nearest are equally near : select the one with the LSB equal to 0

#### Directed rounding

- 3 user-selectable directed rounding modes

- Round toward +oo, -oo or 0

### Usage

• Program through FPU configuration registers

## Floating-point operations

- Add

- Subtract

- Multiply

- Divide

- Remainder

- Square root

## Floating-point format conversion <sup>92</sup>

- Floating-point and Integer

- Round-floating point number to integer value

- Binary-Decimal

- Comparison

#### Invalid operation

- Resulting in a NaN

- Division by zero

#### Overflow

• The result depend of the rounding mode and can produce a +/-oo or the +/-Max value to be written in the destination register

#### Underflow

• Write the denormalize number in the destination register

### Inexact result

Caused by rounding

### Exception handling 94

• A **TRAP** can be requested by the user for any of the 5 exception with a specific handler

The TRAP handler can return a value to be used instead of the exceptional operation result

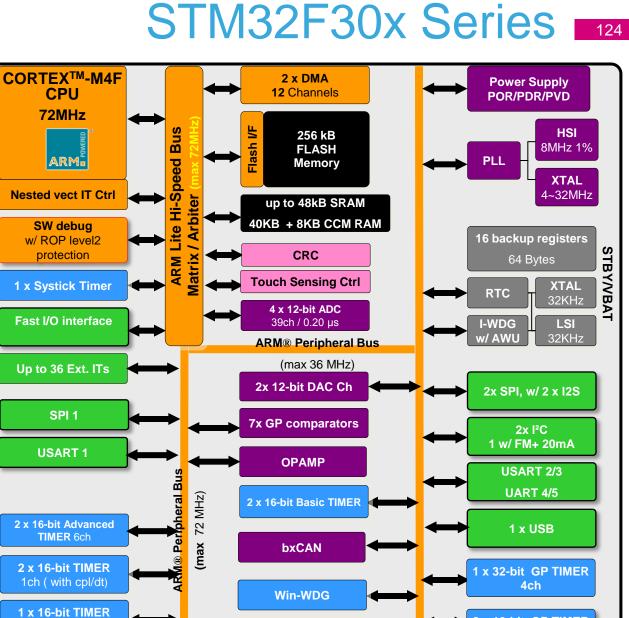

#### ARM 32-bit Cortex-M4F CPU

- **Operating Voltage:**

- VDD = VDD = 2.0 V to 3.6 V or 1.8V + /8%

- VBAT = 1.8 V to 3.6 V

- Safe Reset System (Integrated Power On Reset (POR)/Power Down Reset (PDR) + Programmable voltage detector (PVD))

- Embedded Memories:

- FLASH: up 256 Kbytes

- SRAM: up 48 Kbytes

- **CRC** calculation unit •

- 2 x DMA: 12 channels . •

- Power Supply with software configurable • internal regulator and low power modes.

- Low Power Modes with Auto Wake-up

- Low power calendar RTC with 64 bytes of • backup registers

- Up to 72 MHz frequency managed & monitored • by the Clock Control w/ Clock Security System

- **Rich set of peripherals & IOs**

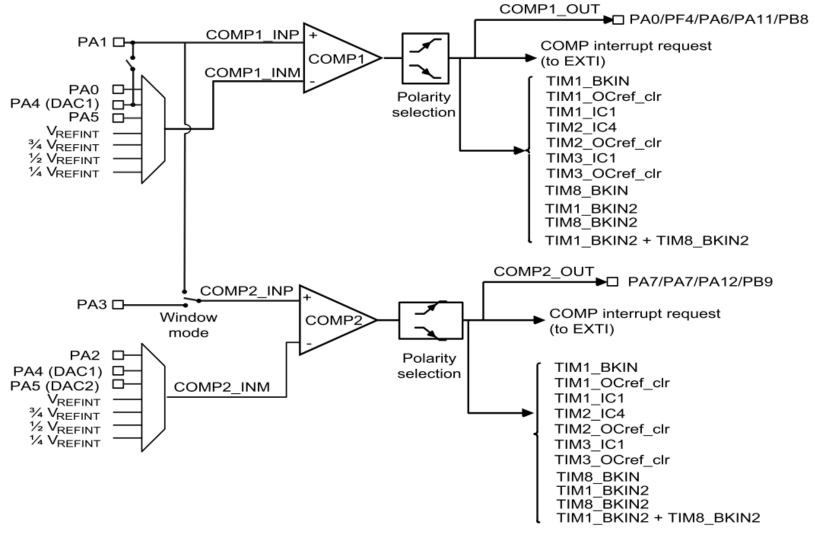

- 2× 12-bit DAC channels with output buffer

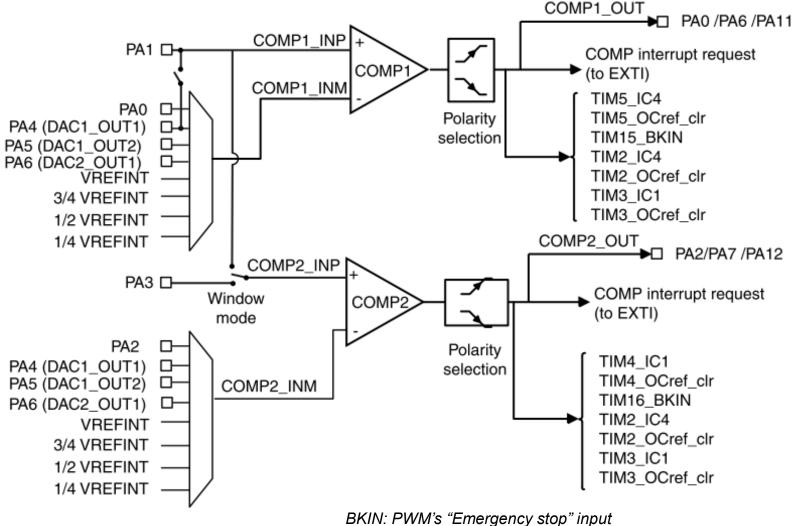

- 7 general purpose comparators (Window mode and wakeup from low-power mode)

- 4 operational amplifiers

- **Dual Watchdog Architecture**

- 13 Timers w/ advanced control features (including 1 Cortex SysTick timer and 2 WDGs timers)

- 14 communication Interfaces

- Up to 88 fast I/Os all mappable on external interrupts/event

- 4x12-bits 5Msps ADC w/ up to 39 external channels + Temperature sensor/ voltage reference/VBAT measurement

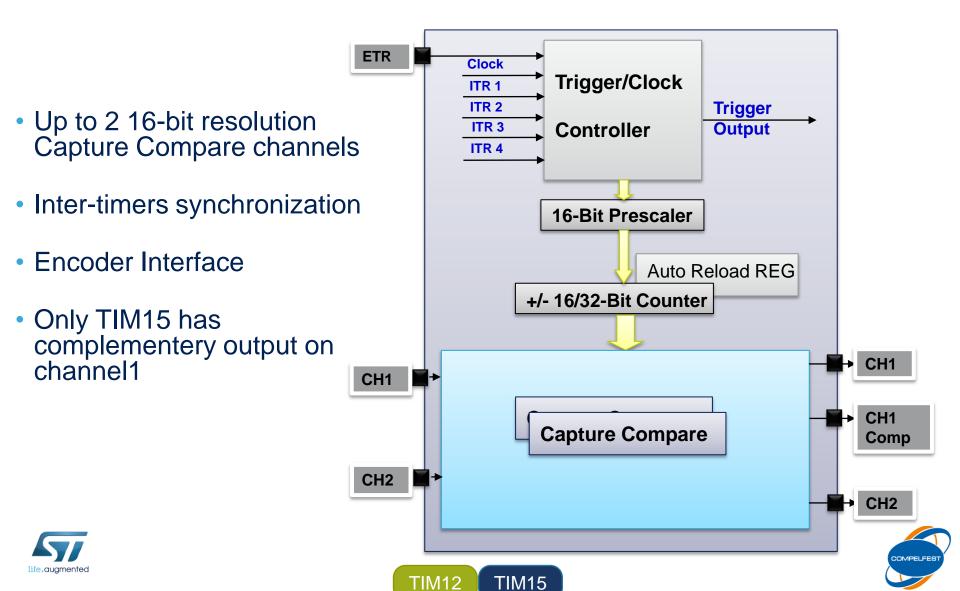

2ch (1ch w/ cpl/dt)

2 x 16-bit GP TIMER

4ch

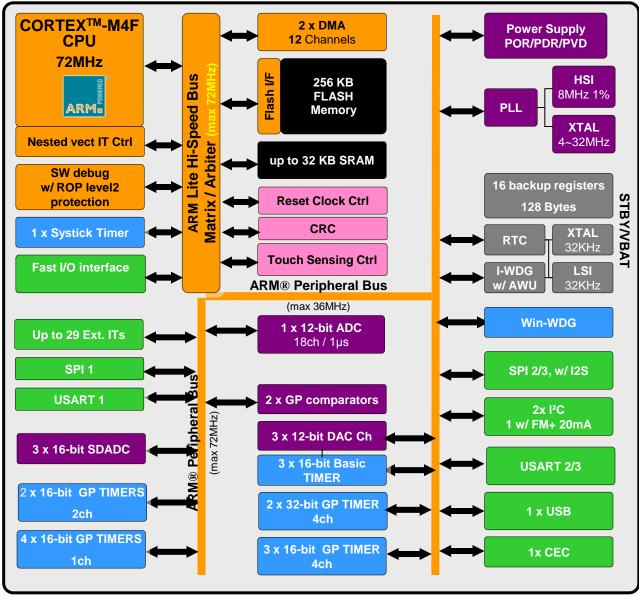

- ARM 32-bit Cortex-M4F CPU

- Operating Voltage:

- VDD = 2.0 V to 3.6 V or 1.8V +/8%

- VBAT = 1.8 V to 3.6 V

- Safe Reset System (Integrated Power On Reset (POR)/Power Down Reset (PDR) + Programmable voltage detector (PVD))

- Embedded Memories:

- FLASH: up 256 Kbytes

- SRAM: up 32Kbytes

- CRC calculation unit

- 2 x DMA: 12 Channels

- Power Supply with software configurable internal regulator and low power modes.

- Low Power Modes with Auto Wake-up

- Low power calendar RTC with 128 bytes of backup registers

- Up to 72 MHz frequency managed & monitored by the Clock Control w/ Clock Security System

- Rich set of peripherals & IOs

- 3 × 12-bit DAC channels with output buffer

- 2 general purpose comparators (Window mode and wakeup from lowpower mode)

- Dual Watchdog Architecture

- 17 Timers (including Cortex SysTick and WDGs)

- 14 communication Interfaces

- Up to 84 fast I/Os all mappable on external interrupts/event

- 1 x12-bits SAR ADC w/ up to 18 external channels .

- 3 x 16-bit Sigma-Delta ADC with conversion speed up to 50 ksps and up to 19 single/ 10 diff channels

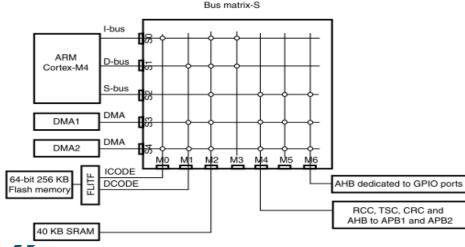

## System Architecture

#### In STM32F37x

- Five masters:

- Cortex-M4F core I-bus

- Cortex-M4F core D-bus

- Cortex-M4F core S-bus

- GP-DMA1 and GP-DMA2 (general-purpose DMAs)

- Five slaves:

- Internal SRAM

- Internal Flash memory

- AHB to APBx (APB1 or APB2), which connect all the APB peripherals

- AHB dedicated to GPIO ports

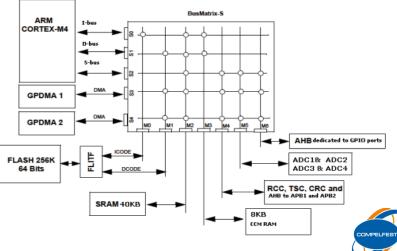

- Five masters:

- Cortex-M4 core I-bus

- Cortex-M4 core D-bus

- Cortex-M4 core S-bus

- GP-DMA1 and GP-DMA2 (general-purpose DMAs)

- Seven slaves:

- Internal SRAM on the Dcode

- Internal SRAM on the ICode (CCM RAM)

- Internal Flash memory

- AHB to APBx (APB1 or APB2), which connec all the APB peripherals

- AHB dedicated to GPIO ports

- ADCs 1,2,3 and 4.

### **Memory Mapping and Boot Modes**

- Addressable memory space of 4 Gbytes

- FLASH : up to 256 Kbytes

- RAM:

life.gugmented

- Up to 40 (F30x) and 32 (F37x) Kbytes SRAM with HW parity check

- Up to 8 Kbytes CCM RAM with HW parity check (STM32F30xonly)

- **0xFFFF FFFF** Reserved 0xE010 0000 Cortex-M4 internal peripherals 0xE000 0000 0x1FFF FFFF Reserved 0x1FFF F80C Option Bytes Reserved 0x1FFF F800 System Memory 0x1FFF EC00 Reserved 0x0804 0000 0x4800 17FF Peripherals Flash 0x0800 0000 0x4000 0000 Reserved SRAM 0x2000 0000 0x0001 0000 Memory type CODE depending on boot 0x0000 0000 0x0000 0000 configuration

- Boot modes

- Depending on the Boot configuration, Embedded Flash memory, System memory or Embedded SRAM memory is aliased at @0x00 thanks to memory remapping bits in SYSCFG registers.

- Even when aliased, these memories are still accessible from their original memory space.

- The boot configuration is defined with **BOOT0 pin** and **BOOT1 bit** in USER Option Byte.

| BOOT Mode<br>Selection |       | Boot Mode        | Aliasing                                |  |  |

|------------------------|-------|------------------|-----------------------------------------|--|--|

| BOOT1                  | воото |                  |                                         |  |  |

| x                      | 0     | User Flash       | User Flash is selected as boot space    |  |  |

| 1                      | 1     | System<br>memory | SystemMemory is selected as boot space  |  |  |

| 0                      | 1     | Embedded<br>SRAM | Embedded SRAM is selected as boot space |  |  |

• **System memory** : contains the Bootloader used to re-program the FLASH through USART or USB .

• **Boot from SRAM :** In the application initialization code you have to Relocate the Vector Table in SRAM using the NVIC Exception Table and Offset register.

4 bits per word for parity check

### **Flash Features Overview**

#### • Flash general features:

- Up to 256 KBytes

- 128 pages of 2KBytes size

- Access time: 35ns

- Half word (16-bit) program time: 52.5µs (Typ)

- Page erase time and Mass erase time: 20ms (Min), 40ms (Max)

#### Flash interface features:

- Read Interface with pre-fetch buffer

- Option Bytes loader

- Flash program/erase operations

- Types of Protection:

- Readout protection: Level 0, Level 1 and Level 2

- Write Protection

## Flash Memory Organization

- Main memory block containing 128 pages of 2Kbyte each.

- Information block contains the system memory and option bytes, is divided into two parts:

- System Memory

- 8 KB size

- contains the bootloader which is used to reprogram the Flash memory through USART1, USART2 or USB.

- used to boot the device in System memory boot mode.

- programmed by ST when the device is manufactured, and protected against unwanted write/erase operations.

- 8 Option bytes : Can be read from the memory location starting from 0x1FFFF800 or from the Option byte register (FLASH\_OBR) in the Flash memory interface register area.

- 4 for write protection

- 1 for read protection

- 1 for device configuration:

- IWDG HW/SW mode

- Reset when entering STANDBY mode

- Reset when entering STOP mode

- VDDA supervisor

- BOOT1

- SRAM parity check

- 2 For User Data (To store Security IDs, etc.)

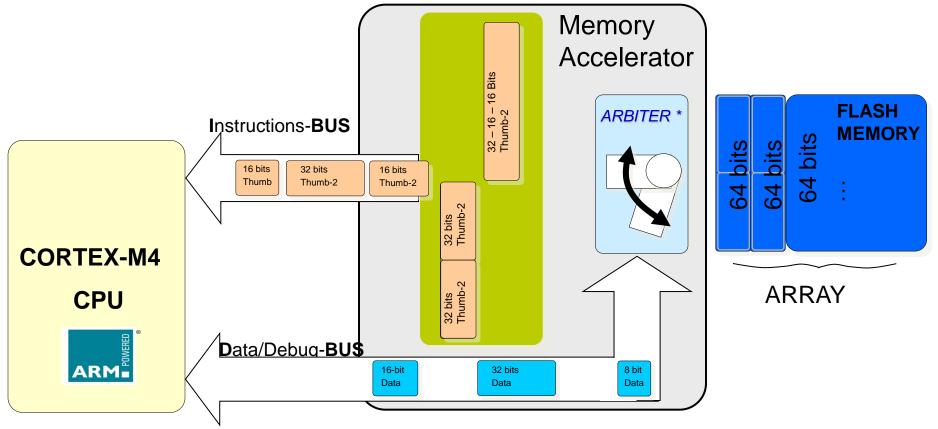

## Flash memory prefetch controller

- Mission: Support 72 MHz operation directly from Flash memory

- 64-bits wide Flash with Prefetch (2 x 64bits buffers).

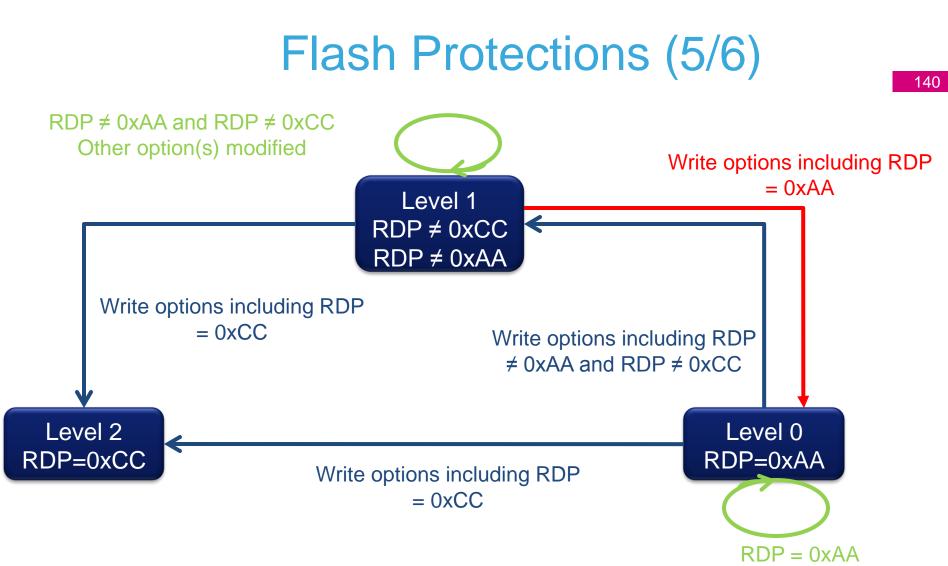

### Flash protections (1/6)

- Two kinds of protections are available:

- Write protection to avoid unwanted writings

- Readout protection to avoid piracy: Level 0, Level 1 and Level 2 (No debug)

- Both are activated by setting option bytes

#### Write protection

- The write protection is implemented with a choice of protecting 2 pages (4K) at a time

- 4 options bytes are used to protect all the 256KBytes main Flash program memory

- Any programming or erase of a protected page is discarded and the Flash will return protection error flag in the FLASH\_SR status register

- Un-protection

- Erase the corresponding bit on WRPx option bytes, x = 0..3.

- Reset the device (POR Reset) or set the FORCE\_OPTLOAD bit to re-load the options bytes for disabling any write protection.

- The write protection bit values are visible also through FLASH\_WRPR write protection register.

## Flash Protections (2/6)

#### Read protection

- The read protection is activated by setting the RDP option byte and then, by applying POR reset or using FORCE\_OPTLOAD bit from FLASH\_CR register to reload the new RDP option byte.

- Three levels of protection from no protection (Level 0) to maximum protection (Level 2 or No debug)

| RDP byte value                | RDP complement value                                     | Read protection level |

|-------------------------------|----------------------------------------------------------|-----------------------|

| 0xAA                          | 0x55                                                     | Level 0               |

| Any value but 0xAA or<br>0xCC | Any value (not necessarily complement) but 0x55 and 0x33 | Level 1               |

| 0xCC                          | 0x33                                                     | Level 2 (No debug)    |

#### • Readout protection Level 0

- No read protection

- All operations (if no write protection is set) from/to the Flash, option byte or the RTC Backup registers are possible in all boot configurations (Flash user boot, boot RAM, boot loader or debug).

## Flash Protections (3/6)

#### Readout protection Level 1

- When this protection is enabled :

- User mode: Code executing in user mode can access main Flash memory and option bytes with all operations.

- Debug, boot RAM and boot loader modes: The main Flash memory and backup registers (RTC\_BKPxR in RTC) are totally inaccessible in these modes, a simple read access generates a bus error and a Hard Fault interrupt. Any attempted program/erase operations sets the PGERR flag.

#### • Un-protection:

When the RPD is reprogrammed to the value 0xAA to move back to Level 0, a Mass erase of the main Flash memory is performed and the backup registers (RTC\_BKPxR in RTC) are reset.

## Flash Protections (4/6)

- Readout protection Level 2 (No debug)

- When This protection is enabled :

- All protections provided by Level 1 are active.

- Boot from RAM, boot from system memory and all debug features (serialwire) are disabled.

- Option bytes can no longer be changed except in user mode but not totally; RDP option byte cannot be programmed/erased and other option bytes can only be programmed (not erased).

- Un-protection:

- Not possible :level 2 cannot be removed at all: it is an irreversible operation.

Other option(s) modified

Option byte write (RDP level increase) includes: Option byte erase and New option byte programming Option byte write (RDP level decrease) includes: Option byte erase, New option byte programming and Mass Erase Option byte write (RDP level identical) includes : Option byte erase and New option byte programming

## Flash Protections (6/6)

Access status versus protection level and execution modes :

| Area                | Protection<br>level | User execution |       | Debug, boot from RAM or<br>boot from system memory<br>(loader) |      |       |       |

|---------------------|---------------------|----------------|-------|----------------------------------------------------------------|------|-------|-------|

|                     |                     | Read           | Write | Erase                                                          | Read | Write | Erase |

| Main<br>memory      | 1                   | Yes            | Yes   | Yes                                                            | No   | No    | No    |

|                     | 2                   | Yes            | Yes   | Yes                                                            | N/A  | N/A   | N/A   |

| System<br>memory    | 1                   | Yes            | No    | No                                                             | Yes  | No    | No    |

|                     | 2                   | Yes            | No    | No                                                             | N/A  | N/A   | N/A   |

| Option<br>bytes     | 1                   | Yes            | Yes   | Yes                                                            | Yes  | Yes   | Yes   |

|                     | 2                   | Yes            | Yes   | No                                                             | N/A  | N/A   | N/A   |

| Backup<br>registers | 1                   | Yes            | Yes   | N/A                                                            | No   | No    | N/A   |

|                     | 2                   | Yes            | Yes   | N/A                                                            | N/A  | N/A   | N/A   |

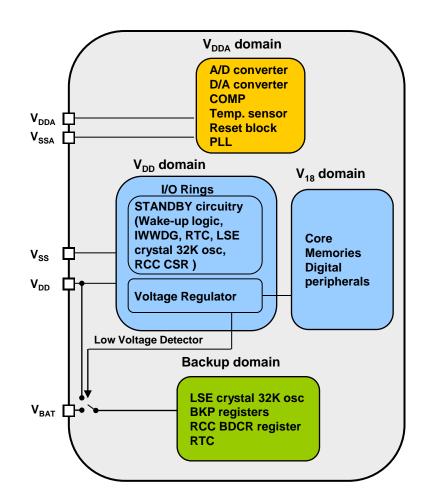

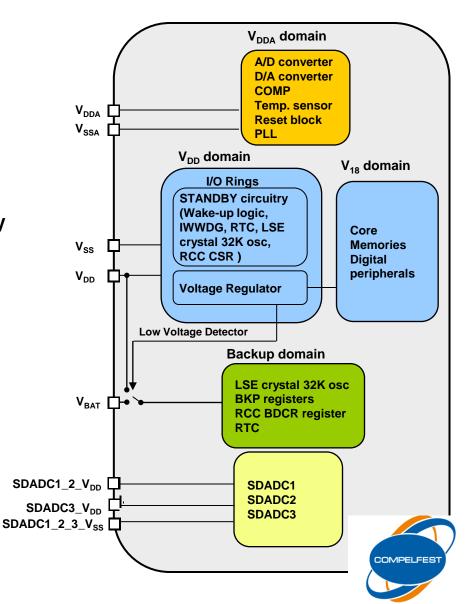

## SRM32F30x Power Supply

- Power Supply Schemes

- VDD = 2.0 to 3.6 V : External Power Supply for I/Os (or VDD = 1.8 +/- 8%: %: External Power Supply for I/Os with internal regulator is OFF.)

- VDDA = 2.0 to 3.6 V: External Analog Power supplies for ADC,DAC, Reset blocks, RCs and PLL.

- → DAC working only if VDDA >=2.4 V

- VBAT = 1.65V to 3.6 V: For Backup domain when VDD is not present.

- Power pins connection:

- VDD and VDDA can be provided by a separated power supply source.

- VSS and VSSA must be tight to ground

## SRM32F37x Power Supply

#### **Power Supply Schemes**

- VDD = 2.0 to 3.6 V : External Power Supply for I/Os (or VDD = 1.8 +/- 8%: %: External Power Supply for I/Os with internal regulator is OFF.)

- VDDA = 2.0 to 3.6 V: External Analog Power supplies for ADC,DAC, Reset blocks, RCs and PLL.

- → ADC and DAC working only if VDDA >=2.4 V

- VBAT = 1.65V to 3.6 V: For Backup domain when VDD is not present.

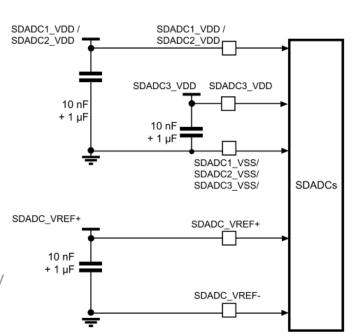

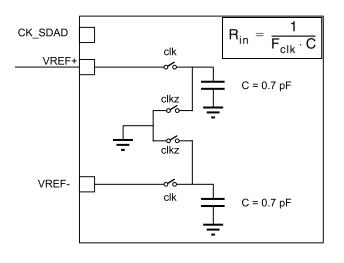

- SDADCx\_VDD = 2.2 to 3.6V : External Analog Power supplies for SDADCs with:

- Power pins connection:

- VDD and VDDA can be provided by a separated power supply source.

- VSS, VSSA and SDADCx\_VSS must be tight to ground

- The SD1\_SD2\_VDD and SD3\_VDD can be different from VDD, VDDA and from one another.

145

### Power Sequence 146

- When VDD power supply source is different from VDDA power supply source (VDD < VDDA)</li>

- The VDDA voltage level must be always greater or equal to the VDD voltage

- During power-on, the VDDA must be provided first (before VDD)

- During power-off, it is allowed to have temporarily VDD > VDDA, but the voltage difference must be <0.4V</li>

- could be maintained by an external Schottky diode

- When SDADCx power supply is different from VDDA, VDD power supply and from one another:

- SDADCx\_VDD <= VDDA

- SDADC1\_VDD/SDADC2\_VDD <= SDADC3\_VDD

- SDADC3\_VDD must start before or at the same time as SD12\_VDD

### Supply monitoring and Reset circuitry

- The STM32F3xx POR / PDR circuitries are always active and monitor two supply voltages: VDD and VDDA.

- The POR supervisor circuit monitors only **VDD**

- The PDR supervisor circuit monitors **VDD** and **VDDA**

- The PDR supervisor on VDDA can be disabled by programming Option byte.

- Programmable Voltage Detection (PVD) Can be ON/OFF.

- The PVD enable/disable is controlled by software via a dedicated bit (PVDE).

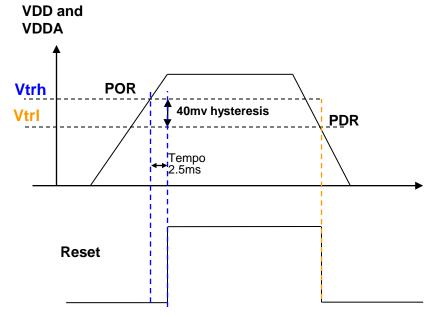

### Power On Reset / Power Down Reset

- Two Integrated POR / PDR circuitries guarantees proper product reset when voltage is not in the product guaranteed voltage range (2V to 3.6V)

- No need for external reset circuit

POR and PDR have a typical hysteresis of 40mV

Vtrl min 1.8V / Vtrh max 2V

• The PDR detector monitors VDD and also VDDA (if kept enabled in the option bytes). The POR detector monitors only VDD.

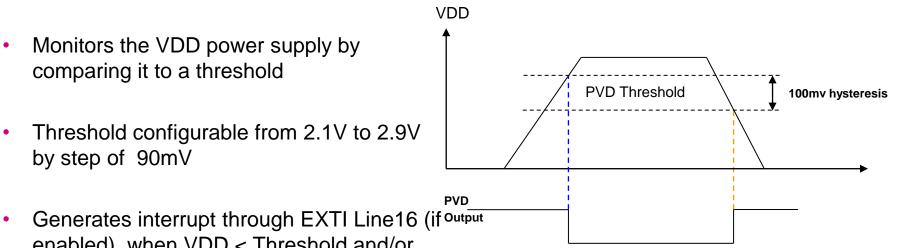

# Programmable Voltage Detector (PVD)

- Programmable Voltage Detector

- Enabled by software

- enabled) when VDD < Threshold and/or</li>

VDD > Threshold

→ Can be used to generate a warning

- Can be used to generate a warning message and/or put the MCU into a safe state

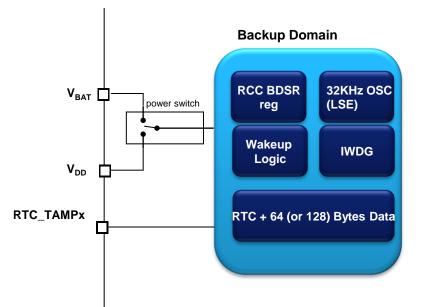

## Backup Domain 150

- Backup Domain contains

- Low power calendar RTC (Alarm, periodic wakeup from Stop/Standby)

- 64 and 128 Bytes Data RTC registers in STM32F30x and STM32F37x respectively.

- Separate 32kHz Osc (LSE) for RTC

- RCC BDSR register: RTC clock source selection and enable + LSE config

- Arrow Reset only by RTC domain RESET

- VBAT independent voltage supply

- Automatic switch-over to VBAT when VDD goes lower than PDR level

- No current sunk on VBAT when VDD present.

- 2 x Tamper events detection: resets all user backup registers

- TimeStamp event detection.

## Low Power Modes (1/4) 151

#### • SLEEP Mode: Core stopped, peripherals kept running

- Entered by executing special instructions

- WFI (Wait For Interrupt)

- Exit: any peripheral interrupt acknowledged by the Nested Vectored Interrupt Controller (NVIC)

- WFE (Wait For Event)

- An *event* can be an interrupt enabled in the peripheral control register but NOT in the NVIC or an EXTI line configured in event mode

- Exit: as soon as the event occurs → No time wasted in interrupt entry/exit

- Two mechanisms to enter this mode

- Sleep Now: MCU enters SLEEP mode as soon as WFI/WFE instruction are executed

- · Sleep on Exit: MCU enters SLEEP mode as soon as it exits the lowest priority ISR

- To further reduce power consumption you can save power of unused peripherals by gating their clock

# Low Power Modes (2/4)

- If the RTC and IWDG are running, they are not stopped in STOP (either as their clock sources)

- To further reduce power consumption, the Voltage Regulator can be put in Low Power mode

Wake-up sources:

- WFI was used for entry: any EXTI Line configured in Interrupt mode (the corresponding EXTI Interrupt vector must be enabled in the NVIC)

- WFE was used for entry: any EXTI Line configured in event mode

- EXTI line source can be: one of the 16 external lines, PVD output, RTC alarm, COMPx, I2Cx, USARTx or the CEC (\*).

- The I2Cx, USARTx, CEC (\*) can be configured to enable the HSI RC oscillator for processing incoming data. If this is used, <u>the voltage regulator should not be put in the low-power mode but kept</u> <u>in normal mode.</u>

- →After resuming from STOP the clock configuration returns to its reset state (HSI used as system clock).

(\*): CEC is available in STM32F37x only.

152

# Low Power Modes (3/4) 153

#### **STANDBY Mode**: Voltage Regulator off, the entire V18 domain is powered off.

- SRAM and register contents are lost except registers in the Backup domain and STANDBY circuitry

- PLL, the HSI RC and the HSE crystal oscillators are also switched off.

- RTC and IWDG are kept running in STANDBY (if enabled)

- In STANDBY mode all IO pins are high impedance and non-active except:

- Reset pad (still available)

- RTC pins (if configured)

- PC14 & PC15 could be forced to output high/low in RTC registers

- WKUPx pins (if enabled)

#### Wake-up sources:

- WKUPx pins rising edge

- RTC alarm and tamper events

- External reset in NRST pin

- IWDG reset

- → After wake-up from STANDBY mode, program execution will restart in the same way as after a RESET.

### STM32F3xx Low Power modes 154

| Mode name                                      | Entry                                                         | Wakeup                                                                                                  | Effect on<br>1.8V<br>domain<br>clocks                                   | Effect on<br>VDD<br>domain<br>clocks | Voltage<br>regulator                                           | IO state                                  | Wakeup latency                                                             |

|------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------|

|                                                | WFI                                                           | Any interrupt                                                                                           | CPU CLK                                                                 |                                      |                                                                |                                           |                                                                            |

| SLEEP,<br>SLEEP now<br>or<br>SLEEP on-<br>exit | WFE                                                           | Wake-up event                                                                                           | OFF<br>no effect on<br>other<br>clocks or<br>analog<br>clock<br>sources | None                                 | ON                                                             | All I/O pins<br>keep the same             | None                                                                       |

| STOP                                           | PDDS,<br>LPSDSR<br>bits +<br>SLEEPDEEP<br>bit +<br>WFI or WFE | Any EXTI line<br>(configured<br>in the EXTI registers,<br><u>internal</u> and <u>external</u><br>lines) | All 1.8V<br>domain                                                      |                                      | ON, in low<br>power<br>mode<br>(dependin<br>g<br>on<br>PWR_CR) | state as in the<br>Run mode               | HSI RC wakeup<br>time + regulator<br>wakeup time<br>from Low-power<br>mode |

| STANDBY                                        | PDDS bit +<br>SLEEPDEEP<br>bit +<br>WFI or WFE                | WKUP pin rising edge,<br>RTC alarm, RTC tamper<br>event, external reset in<br>NRST pin, IWDG reset      | clocks<br>OFF                                                           | oscillator<br>s<br>OFF               | OFF                                                            | all I/O pins are<br>high impedance<br>(*) | Reset phase                                                                |

(\*): Standby mode: all I/O pins are high impedance except:

- Reset pad (still available)

- RTC pins PC14 and PC15 if configured in the RTC registers.

- WKUP pin 1 (PA0) and WKUP pin 2(PC13), if enabled.

# Direct memory access controller (DMA)

### DMA Features 157

- 12 independently configurable channels: hardware requests or software trigger on each channel.

- DMA1: 7 Channels

- DMA2: 5 Channels

- Software programmable priorities: Very high, High, Medium or Low. (Hardware priority in case of equality).

- Programmable and Independent source and destination transfer data size: Byte, Halfword or Word.

- 3 event flags for each channel: DMA Half Transfer, DMA Transfer complete and DMA Transfer Error.

- Memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers and peripheral-to-peripheral transfers.

- Faulty channel is automatically hardware disabled in case of bus access error.

- Programmable number of data to be transferred: up to 65535.

- Support for circular buffer management.

# DMA1 Request Mapping (1/2)

| Periphera<br>I    | Channel 1 | Channel 2 | Channel 3                           | Channel 4                         | Channel 5 | Channel 6             | Channel 7            |

|-------------------|-----------|-----------|-------------------------------------|-----------------------------------|-----------|-----------------------|----------------------|

| ADC               | ADC1      |           |                                     |                                   |           |                       |                      |

| SPI               |           | SPI1_RX   | SPI1_TX                             | SPI2_RX                           | SPI2_TX   |                       |                      |

| USART             |           | USART3_TX | USART3_RX                           | USART1_TX                         | USART1_RX | USART2_RX             | USART2_TX            |

| I2C               |           |           |                                     | I2C2_TX                           | I2C2_RX   | I2C1_TX               | I2C1_RX              |

| TIM1 (*)          |           | TIM1_CH1  | TIM1_CH2                            | TIM1_CH4<br>TIM1_TRIG<br>TIM1_COM | TIM1_UP   | TIM1_CH3              |                      |

| TIM2              | TIM2_CH3  | TIM2_UP   |                                     |                                   |           | TIM2_CH1              | TIM2_CH2<br>TIM2_CH4 |

| TIM3              |           | TIM3_CH3  | TIM3_CH4<br>TIM3_UP                 |                                   |           | TIM3_CH1<br>TIM3_TRIG |                      |

| TIM4              | TIM4_CH1  |           |                                     | TIM4_CH2                          | TIM4_CH3  |                       | TIM4_UP              |

| TIM6 /<br>DAC (*) |           |           | TIM6_UP<br>DAC_CH1 <mark>(1)</mark> |                                   |           |                       |                      |

• (\*) Available on STM32F30x only.

(1) DMA request mapped on this DMA channel only if the corresponding remapping bit is set in the SYSCFG\_CFGR1 register

158

# DMA1 Request Mapping (2/2)

| Peripherals                      | Channel 1                 | Channel 2 | Channel 3             | Channel 4                           | Channel 5           | Channel 6                                     | Channel 7                        |

|----------------------------------|---------------------------|-----------|-----------------------|-------------------------------------|---------------------|-----------------------------------------------|----------------------------------|

| TIM7 / DAC (*)                   |                           |           |                       | TIM7_UP<br>DAC_CH2 <mark>(1)</mark> |                     |                                               |                                  |

| TIM16                            |                           |           | TIM16_CH1<br>TIM16_UP |                                     |                     | TIM16_CH1<br>TIM16_UP<br>(*) <mark>(1)</mark> |                                  |

| TIM17                            | TIM17_CH<br>1<br>TIM17_UP |           |                       |                                     |                     |                                               | TIM17_CH1<br>TIM17_UP<br>(*) (1) |

| TIM18 /<br>DAC<br>channel 3 (**) |                           |           |                       |                                     | TIM18_UP<br>DAC_CH3 |                                               |                                  |

| TIM19 (**)                       | TIM19_CH3<br>TIM19_CH4    | TIM19_CH1 | TIM19_CH2             | TIM19_UP                            |                     |                                               |                                  |

- (\*) Available on STM32F30x only

- (\*\*) Available on STM32F37x only.

- (1) DMA request mapped on this DMA channel only if the corresponding remapping bit is set in the SYSCFG\_CFGR1 register

# **DMA2 Request Mapping**

| Peripherals                   | Channel1            | Channel2                          | Channel3           | Channel4           | Channel5            |

|-------------------------------|---------------------|-----------------------------------|--------------------|--------------------|---------------------|

| ADC                           | ADC2                | ADC4                              | ADC2 (1)<br>SDADC1 | ADC4 (1)<br>SDADC2 | ADC3<br>SDADC3      |

| SPI3                          | SPI3_RX             | SPI3_TX                           |                    |                    |                     |

| UART4(*)                      |                     |                                   | UART4_RX           |                    | UART4_TX            |

| TIM6 / DAC<br>channel 1       |                     |                                   | TIM6_UP<br>DAC_CH1 |                    |                     |

| TIM7 / DAC<br>channel 2       |                     |                                   |                    | TIM7_UP<br>DAC_CH2 |                     |

| TIM8 / DAC<br>(**)            | TIM8_CH3<br>TIM8_UP | TIM8_CH4<br>TIM8_TRIG<br>TIM8_COM | TIM8_CH1           |                    | TIM8_CH2            |

| TIM18 / DAC<br>channel 3 (**) |                     |                                   |                    |                    | TIM18_UP<br>DAC_CH3 |

- (\*) Available on STM32F30x only

- (\*\*) Available on STM32F37x only.

160

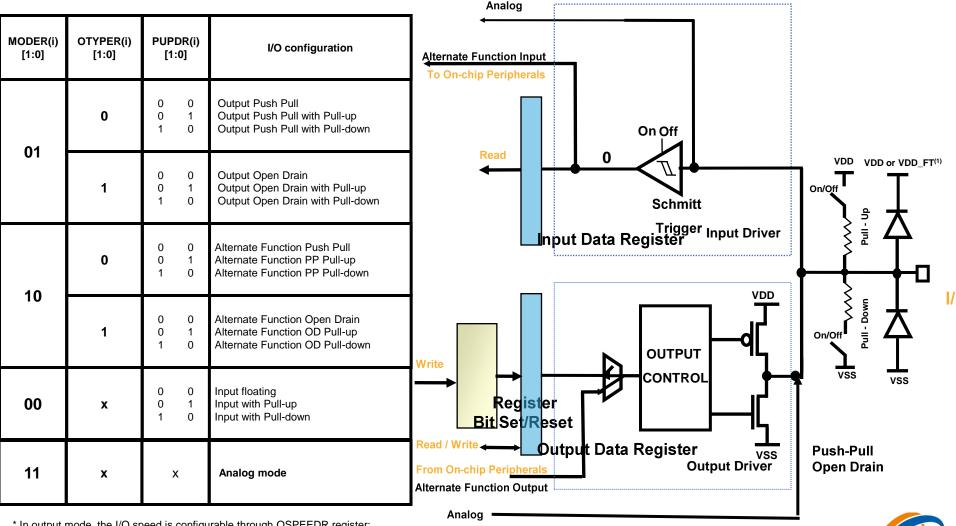

### GPIO features 163

- Up to 84 (in STM32F37x) and 88 (in STM32F30x) multifunction bidirectional I/O ports available on biggest package 100 pin.

- Several I/Os are 5V tolerant (ADC, opamp, comparators pins are not).

- All Standard I/Os are shared in 6 ports: GPIOA, GPIOB, GPIOC, GPIOD, GPIOE, GPIOF.

- Atomic Bit Set and Bit Reset using BSRR and BRR registers

- GPIO connected to AHB bus, max toggling frequency 18 MHz

- Configurable Output slew rate speed up to 50MHz

- Locking mechanism (GPIOx\_LCKR) provided to freeze the I/O configuration

- When the LOCK sequence has been applied on a port bit, it is no longer possible to modify the configuration of the port bit until the next reset (no write access to the CRL and CRH registers corresponding bit).

- Up to 84 (in STM32F37x) and 88 (in STM32F30x) GPIOs can be set-up as external interrupt (up to 16 lines at time) able to wake-up the MC from low power modes.

# GPIO Configuration Modes 164

\* In output mode, the I/O speed is configurable through OSPEEDR register: 2MHz. 10MHz or 50MHz

(1) VDD\_FT is a potential specific to five-volt tolerant I/Os and different from VE

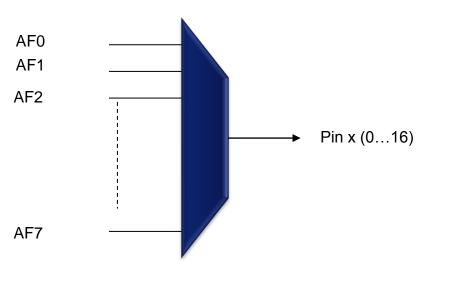

### Alternate Functions features 165

- Most of the peripherals shares the same pin (like USARTx\_TX, TIMx\_CH2, I2Cx\_SCL, SPIx\_MISO, EVENTOUT...)

- Alternate functions multiplexers prevent to have several peripheral's function pin to be connected to a specific I/O at a time.

- Some Alternate function pins are remapped to give the possibility to optimize the number of peripherals used in parallel.

### I/Os special considerations

166

- During and just after reset, the alternate functions are not active and the I/O ports are configured in input floating mode. But, the debug pins (JTAG/SWD) are in AF pull-up/pull-down after reset:

- PA13: JTMS/SWDIO in pull-up

- PA14: JTCK/SWCLK in pull-down

- PA15: JTDI

- PB3: JTDO

- PB4: NJTRST

- Using the HSE or LSE oscillator pins as GPIOs

- When the HSE or LSE oscillator is switched OFF (default state after reset), the related oscillator pins can be used as general purpose IOs.

- When the oscillator is configured in a user external clock mode, only the OSC\_IN or OSC32\_IN pin is reserved for clock input and the OSC\_OUT or OSC32\_OUT pin can still be used as general purpose IOs.

- Using the GPIO pins in the backup supply domain

- The PC13/PC14/PC15 GPIO functionality is lost when the device enters Standby mode. In this case, if their GPIO configuration is not bypassed by the RTC configuration, these pins are set in an analog input mode.

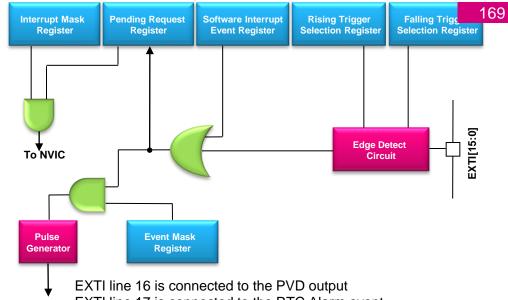

# Extended interrupts and events controller (EXTI)

# **EXTI Features**

- Manages the external and internal asynchronous events/interrupts and generates the event request to the CPU/Interrupt Controller and a wake-up request to the Power Manager

- Some communication peripherals (UART, I2C, CEC <sup>(\*)</sup>, comparators) are able to generate events when the system is in run/sleep mode and also when the <u>system</u> <u>is in stop mode</u> allowing to wake up the system from stop mode.

- These peripherals are able to generate both a synchronized (to the system APB clock) and an asynchronous version of the event.

- All others features are same as STM32F1xx series

- Up to 36 (F30x) 29(F37x) Interrupt/Events requests : Up to 88 (in STM32F30x) and 84 (in STM32F37x) GPIOs can be used as EXTI line(0..15)

- (\*) The CEC is available on STM32F37x only.

EXTI line 17 is connected to the RTC Alarm event EXTI line 18 is connected to USB Device FS wakeup event EXTI line 19 is connected to RTC tamper and Timestamps EXTI line 20 is connected to RTC wakeup EXTI line 21 is connected to Comparator 1 output EXTI line 22 is connected to Comparator 2 output EXTI line 23 is connected to I2C1 wakeup EXTI line 24 is connected to I2C2 wakeup EXTI line 25 is connected to USART1 wakeup EXTI line 26 is connected to USART2 wakeup. EXTI line 27 is connected to CEC wakeup. (STM32F37x only) EXTI line 28 is connected to USART3 wakeup EXTI line 29 is connected to Comparator 3 output (F30x only) EXTI line 30 is connected to Comparator 4 output (F30x only) EXTI line 31 is connected to Comparator 5 output. (F30x only) EXTI line 32 is connected to I Comparator 6 output (F30x only) EXTI line 33 is connected to Comparator 7 output (F30x only) EXTI line 34 is connected to UART4 wakeup. (F30x only) EXTI line 35 is connected to UART5 wakeup. (F30x only)

# RCC introduction 172

#### • Reset:

- Initialize the device

- Wakeup device

- Safety functions (watchdog)

### Clocks:

- Select appropriate clock source:

- Internal

- External

- Select appropriate speed:

- High speed

- Low speed

- Speed regulation

- Modify clock parameters for:

- Core

- Peripherals

- Security functions:

- In case of clock source malfunction

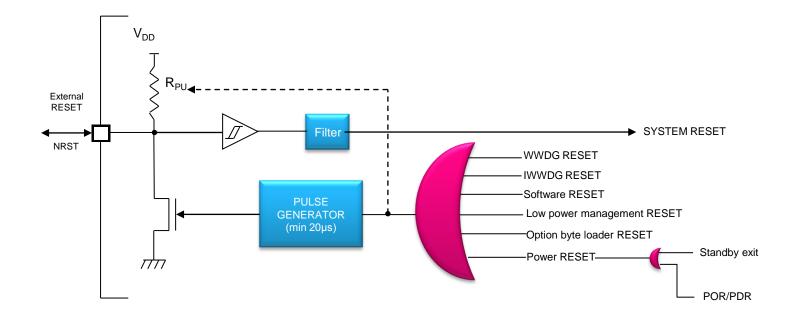

### Reset sources 173

### System RESET

- Resets all registers except some RCC registers and Backup domain

- Sources:

- Low level on the NRST pin (External Reset)

- WWDG & IWWDG end of count condition

- A software reset (through NVIC)

- Low power management reset

- Option byte loader reset (FORCE\_OBL bit)

### Power RESET

- Resets all registers except the Backup domain

- Sources:

- Power On/Power down Reset (POR/PDR)

- Exit from STANDBY

### Backup domain RESET

- Resets in the Backup domain: RTC registers + Backup Registers + RCC\_BDCR register

- Sources:

- BDRST bit in RCC\_BDCR register

- POWER Reset

### Reset block diagram 174

• Reset sources in STM32F3 family and their relation to RESET pin:

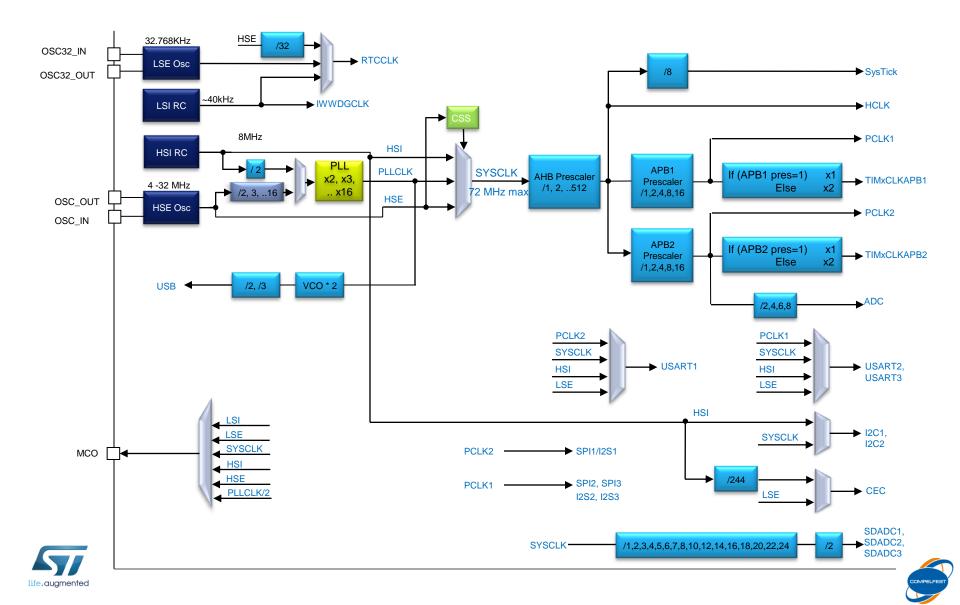

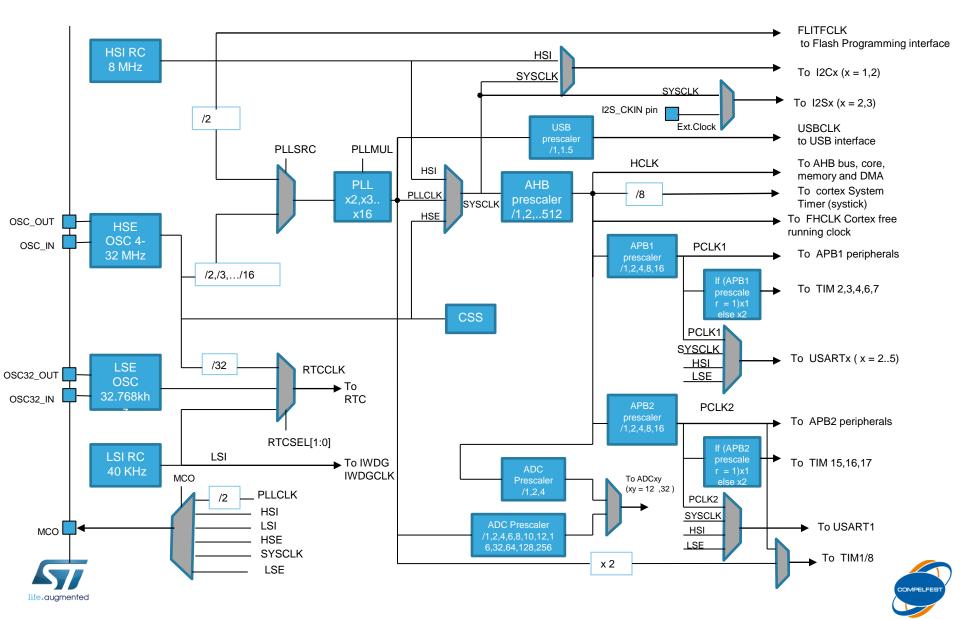

# Clock features (1/2) 175

- System Clock (SYSCLK) sources:

- HSE (High Speed External oscillator or crystal)

- 4MHz to 32MHz,

- can be bypassed by user clock

- HSI (High Speed Internal RC):

- factory trimmed internal RC oscillator 8MHz +/- 1%

- PLL x2, x3, .. x16

- From HSE or HSI/2

- 16MHz 72MHz output

#### Additional clock sources:

- LSI (Low Speed Internal RC):

- ~40kHz internal RC

- LSE (Low Speed External oscillator):

- 32.768kHz

- can be bypassed by user clock

- Configurable driving strength (power/robustness compromise)

# Clock features (2/2) 176

- Clock-out capability on the MCO:

- LSI, LSE, SYSCLK, HSI, HSE, PLL/2

- Clock Security System (CSS) to switch to backup clock:

- In case of HSE clock failure

- Enabled by SW w/ interrupt capability linked to NMI

- Could generate BREAK for Timers

- RTC Clock sources:

- LSE, LSI and HSE/32

- USART, I2C & CEC have multiple possible clock sources:

- Possibility to wakeup device if there is no system clock:

- For USART: HSI, LSE

- For I2C: HSI

- For HDMI-CEC: LSE, HSI

### Clock scheme STM32F37x 177

### Clock scheme STM32F30x 178

## HSI/LSI/ext. clock measurement 179

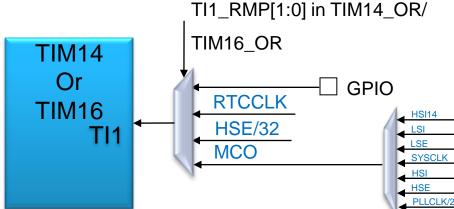

- TIM14 (in F37x) and TIM16 (in F30x) input capture can be triggered by: TI1\_RMP[1:0

- GPIO pin

- RTCCLK

- HSE/32

- MCO output

- Purposes:

- **Measure HSI frequency** using the precise LSE clock. HSI is used as system clock. Knowing the (more precise) LSE frequency we can determine the HSI frequency.

- **Measure the LSI frequency** using HSE or HSI. To fine tune IWWDG and/or RTC timing (if LSI used as RTC clock).

- Have rough indication of the frequency of external crystal by comparing HSI and HSE/32

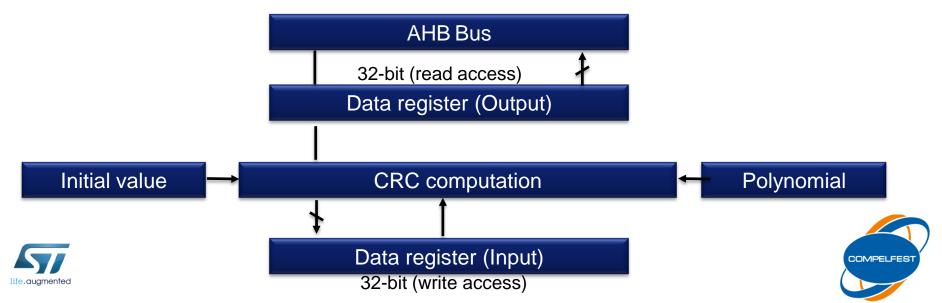

# CRC Introduction 1/2 182

- CRC-based techniques are used to verify data integrity (communications)

- In functional safety standards (such as EN/IEC 60335-1), CRC peripheral offers a means of verifying the embedded Flash memory integrity

- Single input/output 32-bit data register, but handles 8,16, 32-bits input data size

- CRC computation done in 4 AHB clock cycles (HCLK) maximum

- General-purpose 8-bit register (can be used for temporary storage)

# CRC Introduction 2/2 183

#### • New features:

- Programmable parameters:

- Programmable polynomial:

- By default uses CRC-32 (Ethernet) polynomial: 0x4C11DB7

- Alternatively uses a fully programmable polynomial with programmable size (7, 8, 16, 32 bit)

- Programmable polynomial size (7, 8, 16, 32 bits)

- Programmable CRC initial value (default = 0xFFFF\_FFF)

#### Reversibility option on I/O data

- Input data can be reversed by 8, 16, 32 bit

- Example if input data 0x1A2B3C4D is used for CRC calculation as:

- 0x58D43CB2 with bit-reversal done by byte

- 0xD458B23C with bit-reversal done by half-word

- 0xB23CD458 with bit-reversal done on the full word

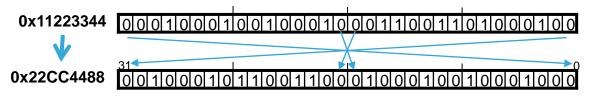

- Output data can be reversed in 32-bit (output register)

- Example on output data 0x11223344:

# CRC Operation 184

#### Operation:

- Each write operation to the data register creates a combination of the previous CRC value (stored in CRC\_DR) and the new one. CRC computation is done on the whole 32bit data word or byte by byte depending on the format of the data being written.

- The duration of the CRC computation depends on input data width:

- 4 AHB clock cycles for 32-bit

- 2 AHB clock cycles for 16-bit

- 1 AHB clock cycles for 8-bit

- Polynomial can be changed after finishing current CRC calculation (or after CRC reset)

- The input and output data can be bit reversed, to manage the various endianness schemes (REV IN [1:0], REV OUT bits).

# DAC introduction 189

#### Interfaces:

- Two 12-bit DAC converters inside STM32F37x:

- DAC1 with 2 DAC output channels

- DAC2 with 1 output channel

- One 12-bit DAC converter inside STM32F30x:

- DAC1 with 2 DAC output channels

#### Features and differences:

- 8-bit or 12-bit mode (left or right data alignment in 12-bit mode)

- Synchronized update capability

- Noise-wave or Triangular-wave generation

- DMA capability for each channel (with DMA underrun error detection)

- External triggers for conversion (Timers, ext. pin, SW trigger)

- Programmable output buffer to drive more current

- Input voltage reference VREF+

- DAC supply requirement: VDDA = 2.4V to 3.6 V

- DAC outputs range: 0 ≤ DAC\_OUTx ≤ VREF+

- Dual DAC channel mode supported by DAC1 only:

- Two channels can be used independently or simultaneously when both channels are grouped together for synchronous update operations (dual mode).

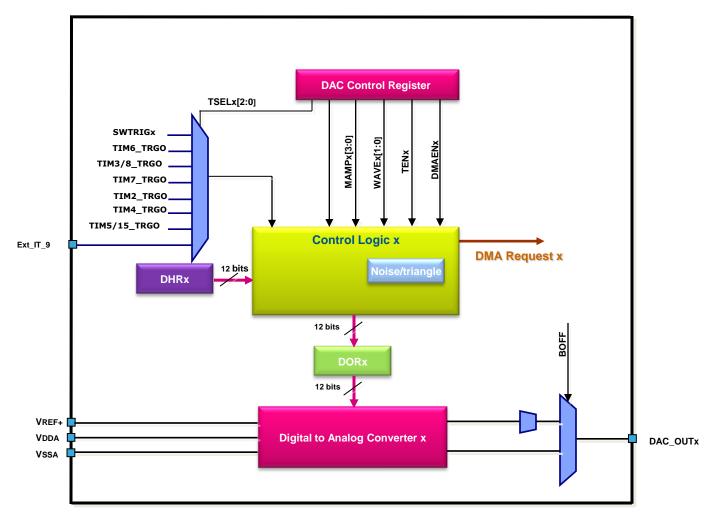

### DACx channel block diagram

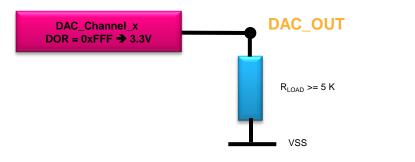

# DAC analog output 191

#### Output voltage:

- Analog output voltage is given by formula:

- DAC Output = V<sub>REF+</sub> \* (DOR / 4095)

- V<sub>REF+</sub> ...... reference voltage (shared with ADC, input pin or shared with VDDA)

- DOR ...... Data output register

#### • Output current:

- Optional output analog buffer (booster) to improve current capability (BOFF bit)

- Without output analog buffer (BOFF bit = 1):

- Rail to rail output: Vout =  $(V_{REF+} + 1LSB) (V_{REF+} 1LSB)$

- Output impedance: 15kΩ

- Min. load for 1% error: >1.5M $\Omega$

- With output analog buffer (BOFF bit = 0):

- Limited output near edges: Vout =  $(200 \text{mV}) (V_{\text{DDA}} 200 \text{mV})$

- Min. load for 1LSB error: >5kΩ

OMPELFE

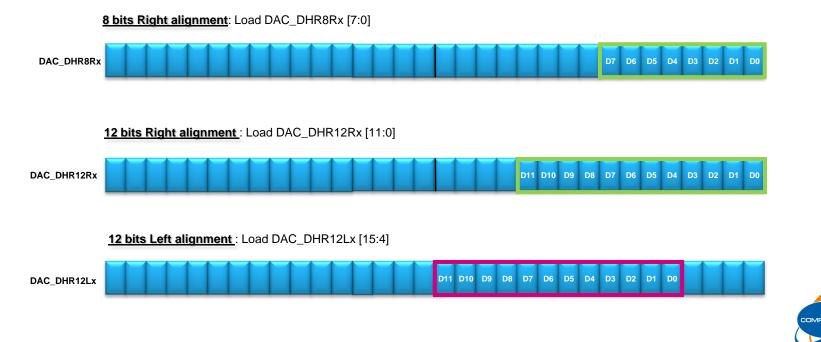

## DAC data format

### • 8-bit mode:

- Always right alignment (in register DAC\_DHR8Rx)

- Also in dual channel mode (register DAC\_DHR8RD)

### • 12-bit mode:

- Right alignment (in register DAC\_DHR12Rx)

- Left alignment (in register DAC\_DHR12Lx)

- Also in dual channel mode (registers DAC\_DHR12RD, DAC\_DHR12LD)

# DAC conversion triggers 193

#### Conversion started (load data to the DORx register) by:

- Automatically (if external trigger disabled TENx) :

- From DAC\_DHRx after one APB1 clock cycle

- Triggered conversion (if external trigger enabled TENx) :

- After three APB1 clock cycles after trigger generated by external trigger (except SWTRIG)

### • Triggers:

- Timers:

- Timer 6 TRGO event

- Timer 3 TRGO event (or Timer 8 as option for STM32F30x)

- Timer 7 TRGO event

- Product dependent :

- For STM32F37x: Timer 5 (for DAC1) / Timer 18 (for DAC2) TRGO event

- For STM32F30x: Timer 15

- Timer 2 TRGO event

- Timer 4 TRGO event

- External pin

- EXTI line9

- Software

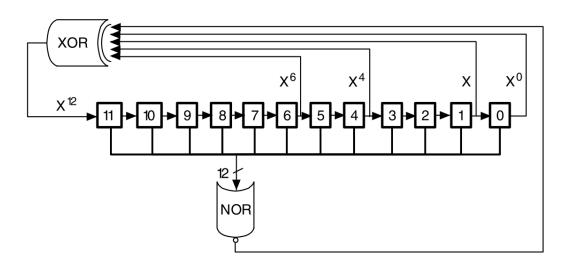

## DAC noise wave generation 194

### Noise generation:

- Based on LFSR (linear feedback shift register):

- Initial value = 0xAAAA

- The LFSR 12bits value can be masked partially or totally

- Anti lock-up mechanism: if LFSR equal to 0 then a 1 is injected on it

- Calculated noise value (updated through external trigger) is added to the DAC\_DHRx content without overflow

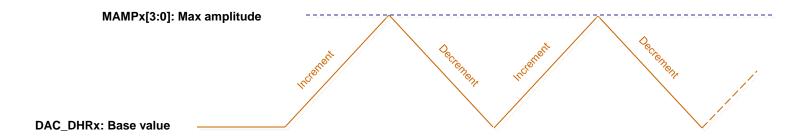

# DAC triangle wave generation 195

#### • Triangle generation:

- Add a small-amplitude triangular waveform on a DC or slowly varying signal: used as basic waveform generator for example

- Calculated triangle value (updated through external trigger) is added to the DAC\_DHRx content without overflow to reach the configurable max amplitude

- Up-Down triangle counter:

- Incremented to reach defined max amplitude value

- · Decremented to return to the initial base value

- Triangle max. amplitude are configurable: (2<sup>N</sup>-1) with N=[1..12]

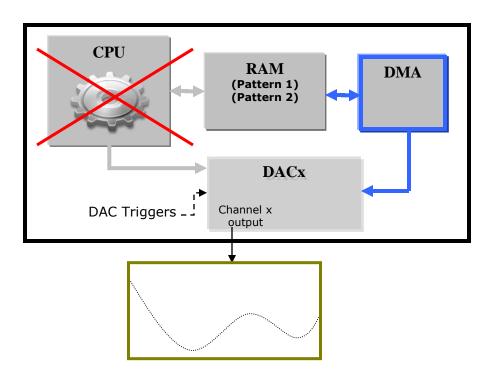

## DAC with DMA 197

- A DAC DMA request is generated when an external trigger occurs:

- The value of the DAC\_DHR register is then transferred to the DAC\_DOR register.

- DMA underrun error detection with interrupt capability

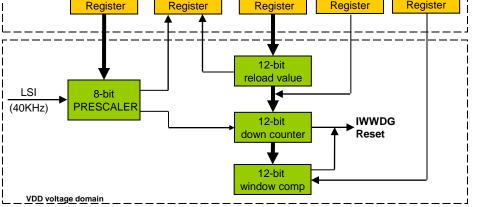

## Independent and System Watchdogs